Physics:Silicon on sapphire

Silicon on sapphire (SOS) is a hetero-epitaxial process for metal–oxide–semiconductor (MOS) integrated circuit (IC) manufacturing that consists of a thin layer (typically thinner than 0.6 µm) of silicon grown on a sapphire (Al2O3) wafer. SOS is part of the silicon-on-insulator (SOI) family of CMOS (complementary MOS) technologies.

Typically, high-purity artificially grown sapphire crystals are used. The silicon is usually deposited by the decomposition of silane gas (SiH4) on heated sapphire substrates. The advantage of sapphire is that it is an excellent electrical insulator, preventing stray currents caused by radiation from spreading to nearby circuit elements. SOS faced early challenges in commercial manufacturing because of difficulties in fabricating the very small transistors used in modern high-density applications. This is because the SOS process results in the formation of dislocations, twinning and stacking faults from crystal lattice disparities between the sapphire and silicon. Additionally, there is some aluminum, a p-type dopant, contamination from the substrate in the silicon closest to the interface.

History

In 1963, Harold M. Manasevit was the first to document epitaxial growth of silicon on sapphire while working at the Autonetics division of North American Aviation (now Boeing). In 1964, he published his findings with colleague William Simpson in the Journal of Applied Physics.[1] In 1965, C.W. Mueller and P.H. Robinson fabricated a MOSFET (metal–oxide–semiconductor field-effect transistor) using the silicon-on-sapphire process at RCA Laboratories.[2]

SOS was first used in aerospace and military applications because of its inherent resistance to radiation. More recently, patented advancements in SOS processing and design have been made by Peregrine Semiconductor, allowing SOS to be commercialized in high-volume for high-performance radio-frequency (RF) applications.

Circuits and systems

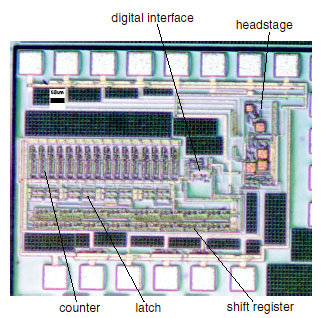

The advantages of the SOS technology allow research groups to fabricate a variety of SOS circuits and systems that benefit from the technology and advance the state-of-the-art in:

- analog-to-digital converters (a nano-Watts prototype was produced by Yale e-Lab)[4][5]

- monolithic digital isolation buffers[6]

- SOS-CMOS image sensor arrays (one of the first standard CMOS image sensor arrays capable of transducing light simultaneously from both sides of the die was produced by Yale e-Lab)[7]

- patch-clamp amplifiers[8]

- energy harvesting devices[9]

- three-dimensional (3D) integration with no galvanic connections

- charge pumps[10]

- temperature sensors[9]

- early microprocessors, such as the RCA 1802

Applications

Silicon on sapphire pressure transducer, pressure transmitter and temperature sensor diaphragms have been manufactured using a patented process by Armen Sahagen since 1985.[11] Outstanding performance in high temperature environments helped propel this technology forward. This SOS technology has been licensed throughout the world. ESI Technology Ltd. in the UK have developed a wide range of pressure transducers and pressure transmitters that benefit from the outstanding features of silicon on sapphire.[12]

Peregrine Semiconductor has used SOS technology to develop RF integrated circuits (RFICs) including RF switches, digital step attenuators (DSAs), phase locked-loop (PLL) frequency synthesizers, prescalers, mixers/upconverters, and variable-gain amplifiers. These RFICs are designed for commercial RF applications such as mobile handsets and cellular infrastructure, broadband consumer and DTV, test and measurement, and industrial public safety, as well as rad-hard aerospace and defense markets.

Hewlett-Packard used SOS in some of their CPU designs, particularly in the HP 3000 line of computers.[13]

Substrate analysis: SOS structure

The application of epitaxial growth of silicon on sapphire substrates for fabricating MOS devices involves a silicon purification process that mitigates crystal defects which result from a mismatch between sapphire and silicon lattices. For example, Peregrine Semiconductor's SP4T switch is formed on an SOS substrate where the final thickness of silicon is approximately 95 nm. Silicon is recessed in regions outside the polysilicon gate stack by poly oxidation and further recessed by the sidewall spacer formation process to a thickness of approximately 78 nm.[citation needed]

See also

References

- ↑ Manasevit, H. M.; Simpson, W. J. (1964). "Single-Crystal Silicon on a Sapphire Substrate". Journal of Applied Physics 35 (4): 1349–51. doi:10.1063/1.1713618. Bibcode: 1964JAP....35.1349M.

- ↑ Mueller, C. W.; Robinson, P. H. (December 1964). "Grown-film silicon transistors on sapphire". Proceedings of the IEEE 52 (12): 1487–90. doi:10.1109/PROC.1964.3436.

- ↑ "e-Lab". http://www.eng.yale.edu/elab/.

- ↑ Culurciello, Eugenio; Andreou, Andreas G. (September 2006). "An 8-bit 800-µW 1.23-MS/s Successive Approximation ADC in SOI CMOS". IEEE Transactions on Circuits and Systems 53 (9): 858–861. doi:10.1109/TCSII.2006.880021. https://e-lab.github.io/data/papers/TCASIIadc06.pdf.

- ↑ Fu, Zhengming; Weerakoon, Pujitha; Culurciello, Eugenio (16 March 2006). "Nano-Watt silicon-on-sapphire ADC using 2C-1C capacitor chain". Electronics Letters 42 (6): 341–3. doi:10.1049/el:20060109. Bibcode: 2006ElL....42..341F. https://e-lab.github.io/data/papers/EL20062c1csadc.pdf.

- ↑ Culurciello, E.; Pouliquen, P.; Andreou, A.G. (21–24 May 2006). "2006 IEEE International Symposium on Circuits and Systems". IEEE International Symposium on Circuits and Systems 2006. pp. 3710–3713. doi:10.1109/ISCAS.2006.1693433. ISBN 0-7803-9389-9.

- ↑ Culurciello, E.; Andreou, A. G. (January 8, 2004). "16×16 pixel silicon on sapphire CMOS digital pixel photosensor array". Electronics Letters 40 (1): 66–68. doi:10.1049/el:20040055. Bibcode: 2004ElL....40...66C. https://e-lab.github.io/data/papers/EL2004_SOSDPS.pdf.

- ↑ Laiwalla, F.; Klemic, K.G.; Sigworth, F.J.; Culurciello, E. (21–24 May 2006). "2006 IEEE International Symposium on Circuits and Systems". IEEE International Symposium on Circuits and Systems 2006. pp. 4054–7. doi:10.1109/ISCAS.2006.1693519. ISBN 0-7803-9389-9.

- ↑ 9.0 9.1 Kaya, T.; Koser, H.; Culurciello, E. (27 April 2006). "A Low-Voltage Temperature Sensor for Micro Power Harvesters in Silicon-on-Sapphire CMOS". Electronics Letters 42 (9): 526–8. doi:10.1049/el:20060867. Bibcode: 2006ElL....42..526K. https://e-lab.github.io/data/papers/EL2006harvest.pdf.

- ↑ Culurciello, Eugenio; Pouliquen, Philippe O.; Andreou, Andreas G. (24 January 2005). "Isolation charge pump fabricated in silicon on sapphire CMOS technology". Electronics Letters 41 (10): 520–592. doi:10.1049/el:20050312. Bibcode: 2005ElL....41..590C. https://e-lab.github.io/data/papers/el2005_isolationcp.pdf.

- ↑ "Silicon-on-Sapphire High Temperature Pressure Transducer Products". https://www.sensonetics.com.

- ↑ "Pressure Sensors, Strain Gauges, Telemetry Systems". http://www.esi-tec.com.

- ↑ Edwards, Richard C. (September 1979). "SOS Technology Yields Low-Cost HP 3000 Computer System". Hewlett-Packard Journal 30 (9): 3–6. https://www.hpl.hp.com/hpjournal/pdfs/IssuePDFs/1979-09.pdf. Retrieved 2021-12-29.

Further reading

- Silicon-on-Sapphire Circuits and Systems, Sensor and Biosensor interfaces. McGraw Hill. 2009. ISBN 978-0-07-160849-7. OCLC 459797166. https://books.google.com/books?id=jeKxNMFb-MAC&pg=PR7.

External links

- Shirriff, Ken (December 2023). "The transparent chip inside a vintage Hewlett-Packard floppy drive". http://www.righto.com/2023/12/HP-silicon-on-sapphire-phi-chip.html.

|