Engineering:Propagation delay

Propagation delay is the length of time taken for a signal to reach its destination. It can relate to networking, electronics or physics. Hold time is the minimum interval required for the logic level to remain on the input after triggering edge of the clock pulse.

Networking

In computer networks, propagation delay is the amount of time it takes for the head of the signal to travel from the sender to the receiver. It can be computed as the ratio between the link length and the propagation speed over the specific medium.

Propagation delay is equal to d / s where d is the distance and s is the wave propagation speed. In wireless communication, s=c, i.e. the speed of light. In copper wire, the speed s generally ranges from .59c to .77c.[1][2] This delay is the major obstacle in the development of high-speed computers and is called the interconnect bottleneck in IC systems.

Electronics

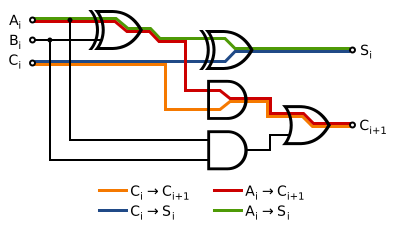

In electronics, digital circuits and digital electronics, the propagation delay, or gate delay, is the length of time which starts when the input to a logic gate becomes stable and valid to change, to the time that the output of that logic gate is stable and valid to change. Often on manufacturers' datasheets this refers to the time required for the output to reach 50% of its final output level when the input changes to 50% of its final input level. Reducing gate delays in digital circuits allows them to process data at a faster rate and improve overall performance. The determination of the propagation delay of a combined circuit requires identifying the longest path of propagation delays from input to output and by adding each tpd time along this path.

The difference in propagation delays of logic elements is the major contributor to glitches in asynchronous circuits as a result of race conditions.

The principle of logical effort utilizes propagation delays to compare designs implementing the same logical statement.

Propagation delay increases with operating temperature, as resistance of conductive materials tends to increase with temperature. Marginal increases in supply voltage can increase propagation delay since the upper switching threshold voltage, VIH (often expressed as a percentage of the high-voltage supply rail), naturally increases proportionately.[3] Increases in output load capacitance, often from placing increased fan-out loads on a wire, will also increase propagation delay. All of these factors influence each other through an RC time constant: any increase in load capacitance increases C, heat-induced resistance the R factor, and supply threshold voltage increases will affect whether more than one time constants are required to reach the threshold. If the output of a logic gate is connected to a long trace or used to drive many other gates (high fanout) the propagation delay increases substantially.

Wires have an approximate propagation delay of 1 ns for every 6 inches (15 cm) of length.[4] Logic gates can have propagation delays ranging from more than 10 ns down to the picosecond range, depending on the technology being used.[4]

Physics

In physics, particularly in the electromagnetic field, the propagation delay is the length of time it takes for a signal to travel to its destination. For example, in the case of an electric signal, it is the time taken for the signal to travel through a wire. See also velocity factor.

See also

- Contamination delay

- Delay calculation

- Latency (engineering)

- Time of flight

- Transmission delay

References

- ↑ "What is propagation delay? (Ethernet Physical Layer)". Ethernet FAQ. 2010-10-21. http://stason.org/TULARC/networking/lans-ethernet/3-11-What-is-propagation-delay-Ethernet-Physical-Layer.html.

- ↑ "Propagation Delay and Its Relationship to Maximum Cable Length". Networking Glossary. http://www.wildpackets.com/resources/compendium/ethernet/propagation_delay.

- ↑ "Logic Signal Voltage Levels". http://www.allaboutcircuits.com/textbook/digital/chpt-3/logic-signal-voltage-levels/.

- ↑ 4.0 4.1 Balch, Mark (2003). Mcgraw Hill - Complete Digital Design A Comprehensive Guide To Digital Electronics And Computer System Architecture. McGraw-Hill Professional. pp. 430. ISBN 978-0-07-140927-8. https://books.google.com/books?id=uFSRT-OIxyoC.