Engineering:PHY

A PHY, an abbreviation for "physical layer", is an electronic circuit, usually implemented as an integrated circuit, required to implement physical layer functions of the OSI model in a network interface controller.

A PHY connects a link layer device (often called MAC as an acronym for medium access control) to a physical medium such as an optical fiber or copper cable. A PHY device typically includes both Physical Coding Sublayer (PCS) and Physical Medium Dependent (PMD) layer functionality.[1]

-PHY may also be used as a suffix to form a short name referencing a specific physical layer protocol, for example M-PHY.

Modular transceivers for fiber-optic communication (like the SFP family) complement a PHY chip and form the PMA sublayer.

Ethernet physical transceiver

The Ethernet PHY is a component that operates at the physical layer of the OSI network model. It implements the physical layer portion of the Ethernet. Its purpose is to provide analog signal physical access to the link. It is usually interfaced with a Media Independent Interface (MII) to a MAC chip in a microcontroller or another system that takes care of the higher layer functions.

More specifically, the Ethernet PHY is a chip that implements the hardware send and receive function of Ethernet frames; it interfaces between the analog domain of Ethernet's line modulation and the digital domain of link-layer packet signaling.[2] The PHY usually does not handle MAC addressing, as that is the link layer's job. Similarly, Wake-on-LAN and Boot ROM functionality is implemented in the network interface card (NIC), which may have PHY, MAC, and other functionality integrated into one chip or as separate chips.

Common ethernet interfaces include fiber, or two to four copper pairs for data communication. However, there now exists a new interface, called Single Pair Ethernet (SPE), which is able to utilize a single pair of copper wires while still communicating at the intended speeds. Texas Instruments DP83TD510E[3] is an example of a PHY which uses SPE.

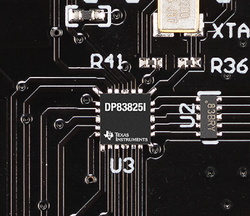

Examples include the Microsemi SimpliPHY and SynchroPHY VSC82xx/84xx/85xx/86xx family, Marvell Alaska 88E1310/88E1310S/88E1318/88E1318S Gigabit Ethernet transceivers, Texas Instruments DP838xx family[4] and offerings from Intel[5] and ICS.[6]

Other applications

- Wireless LAN or Wi-Fi: The PHY portion consists of the RF, mixed-signal and analog portions, that are often called transceivers, and the digital baseband portion that use digital signal processor (DSP) and communication algorithm processing, including channel codes. It is common that these PHY portions are integrated with the medium access control (MAC) layer in system-on-a-chip (SOC) implementations. Similar wireless applications include 3G/4G/LTE, WiMAX and UWB.

- Universal Serial Bus (USB): A PHY chip is integrated into most USB controllers in hosts or embedded systems and provides the bridge between the digital and modulated parts of the interface.

- IrDA: The Infrared Data Association's (IrDA) specification includes an IrPHY specification for the physical layer of the data transport.

- Serial ATA (SATA): Serial ATA controllers use a PHY.

References

- ↑ Mauricio Arregoces; Maurizio Portolani (2003). Data Center Fundamentals. ISBN 9781587050237. https://books.google.com/books?id=DRIryrLoxKkC&q=ethernet+PHY&pg=PA495. Retrieved 2015-11-18.

- ↑ "microcontroller - what is the difference between PHY and MAC chip - Electrical Engineering Stack Exchange". Electronics.stackexchange.com. 2013-07-11. http://electronics.stackexchange.com/questions/75596/what-is-the-difference-between-phy-and-mac-chip.

- ↑ "DP83TD510E Ultra Low Power 802.3cg 10Base-T1L 10M Single Pair Ethernet PHY". https://www.ti.com/lit/ds/symlink/dp83td510e.pdf?ts=1602524952891&ref_url=https%253A%252F%252Fwww.ti.com%252Fproduct%252FDP83TD510E.

- ↑ "Ethernet PHYs". https://www.ti.com/interface/ethernet/phys/overview.html.

- ↑ Intel PHY controllers brochure

- ↑ osuosl.org - ICS1890 10Base-T/100Base-TX Integrated PHYceiver datasheet

it:Livello fisico