Engineering:CMOS amplifiers

CMOS amplifiers are ubiquitous analog circuits which are used in computers, audio systems, smart phones, cameras, telecommunication systems, biomedical circuits and many other systems, and their performance has great impact on the overall specifications of the systems. They take their name from the use of MOSFET (Metal Oxide Semiconductor Field Effect Transistor) as opposite to Bipolar Junction Transistors (BJT). MOSFETS are simpler to fabricate and therefore less expensive than BJT amplifiers, still providing a sufficiently high transconductance to allow the design of very high performance circuits. In high performance CMOS amplifier circuits, transistors are not only used to amplify the signal but are also used as active loads to achieve higher gain and output swing in comparison with resistive loads.[1][2][3] CMOS technology had been primarily introduced to design digital circuits. In the last decades, in order to improve speed, power consumption, required area and other aspects of digital integrated circuits (ICs), the feature size of MOSFET transistors has shrunk (minimum channel length of transistors reduces in newer CMOS technologies). This phenomenon predicted by Gordon Moore in 1975, which is called Moore’s law, and states that in about each 2 years, the number of transistors doubles for the same silicon area of ICs. Progress in memory circuits design is an interesting example to see how process advancement have affected the required size and their performance in the last decades. In 1956, a 5MB Hard Disk Drive (HDD) weighted over a tone,[4] while these days having 50000 times more capacity with a weight of several tens of grams is very common.[5]

While digital ICs have enormously benefited from the feature size shrinking, analog CMOS amplifiers have not gained corresponding advantages due to the intrinsic limitations imposed by an analog design, like the intrinsic gain reduction of short channel transistors which affects the overall gain of amplifier. Novel techniques to achieve higher gain also create new problems, like stability of amplifier for closed-loop applications. In the following, we will address both aspects and summarize few different methods to overcome these problems.

Intrinsic Gain Reduction in Modern CMOS Technologies

Maximum gain of a single MOSFET transistor is called intrinsic gain, and is equal to:

Which gm is the transconductance, and ro is the output resistance of transistor. As a first order approximation, ro is directly proportional to the channel length of transistors. In a single-stage amplifier, one can increase channel length in order to get higher output resistance and gain as well. But, it will also increase parasitic capacitance of transistor, which will limit the bandwidth of amplifier. Channel length of transistors become smaller in modern CMOS technologies, and makes achieving high gain in single-stage amplifier very challenging. In order to achieve high gain, many techniques have been suggested in the literature.[6][7][8] In the following sections, we will have a brief look to different topologies of amplifiers, and their features.

Single-Stage Amplifiers

Telescopic, Folded Cascode (FC), or Recycling FC (RFC) are the most common single stage amplifiers. All these structures use transistors as active loads in order to provide higher output resistance (= higher gain), and output swing. Telescopic amplifier, provides higher gain (due to higher output resistance) and higher bandwidth (due to smaller non-dominant pole at cascode node). In contrast, it has limited output swing and difficulty in implementation of unity-gain buffer. Although FC has lower gain and bandwidth, it can provide higher output swing which is important advantage in modern CMOS technologies, where supply voltage is reduced. Also, since the DC voltage of input and output nodes can be at the same level, it is more suitable for implementation of unity-gain buffer.[3] FC is recently used to implement integrator in a Bio-Nano sensor application.[9][10] Also, it can be used as a stage in multi-stage amplifiers. As an example, FC is used as the input stage of a two-stage amplifier in designing of a potentiostat circuit, which is to measure neuronal activities, or DNA sensing.[11] Also, it can be used to realize transimpedance amplifier (TIA). TIA can be used in amperometric biosensors to measure current of cells or solutions in order to define the characteristics of a device under test[12] In the last decade, circuit designer have proposed different modified versions of FC circuit. RFC is one of the modified versions of FC amplifier, which provides higher gain, higher bandwidth, and also higher slew rate in comparison with FC (for the same power consumption).[13] Recently, RFC amplifier has used in hybrid CMOS-graphene sensor array for subsecond measurement of dopamine.[14] It is used as a low noise amplifier to implement integrator.

Stability

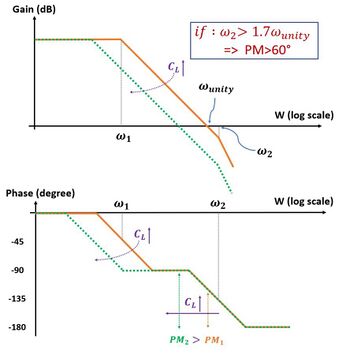

In many applications, amplifier drives capacitor as a load. In some applications, like switched capacitor circuits,the value of capacitive load changes in different cycles. Therefore, it will affect time constant of output node and the frequency response of amplifier. Stable behavior of amplifier for all possible capacitive loads is necessary, and designer must consider this issue during designing of circuit. Designer should ensure that phase margin (PM) of the circuit will be enough for the worst case. In order to have proper circuit behavior and time response, designers usually consider PM of 60 degrees. for higher values of PM, circuit will be more stable, but it will take longer time for output voltage to reach its final value.[1][2][3] In Telescopic, and FC amplifiers, dominant pole is located at the output nodes. Also, there is a non-dominant pole at cascode node.[3] Since capacitive load connected to output nodes, its value will affect the location of the dominant pole. This figure shows how capacitive load affects the location of dominant pole (W1) and stability. Increasing of capacitive load, will move dominant pole toward the origin, and since unity gain frequency (Wunity) is Av (amplifier gain) times of W1, it will also move toward the origin. Therefore, PM will increase, which improves stability. So, if we ensure stability of a circuit for a minimum capacitive load, it will remain stable for larger load values.[2][3] In order to achieve greater than 60 degrees PM, the non-dominant pole (W2) must be greater than 1.7 times of Wunity.

Multi-Stage Amplifiers

In some applications, like switched capacitor filters or integrators, and different types of analog-to-digital converters, having high gain (70-80 dB) is needed, and achieving the required gain sometimes is impossible with single-stage amplifiers.[6] This is more serious in modern CMOS technologies, which transistors have smaller output resistance due to shorter channel length. In order to achieve high gain as well as high output swing, multi-stage amplifiers have been invented. To implement two-stage amplifier, one can use FC amplifier as the first stage and a common source amplifier as the second stage. Also, to implement four-stage amplifier, 3 common source amplifier can be cascaded with FC amplifier.[15] It should be mentioned that to drive large capacitive loads or small resistive loads, the output stage should be class AB.[2] For example, common source amplifier with class AB behavior can be used as the final stage in three-stage amplifier to not only improve drive capability, but also gain.[16] Class AB amplifier can be used as a column driver in LCDs.[17]

Stability in Two-Stage Amplifiers

Unlike single-stage amplifiers, multi-stage amplifiers usually have 3 or more poles and if they used in feedback networks, the closed loop system will probably unstable. In order to have stable behavior in multi-stage amplifiers, it is necessary to use compensation network. The main goal of compensation network is to modify transfer function of the system in such a way to achieve enough PM.[2][3] So, by the use of compensation network, we should get frequency response similar to what we showed for single-stage amplifiers. In single-stage amplifiers, capacitive load is connected to output node which dominant pole happens there, and increasing its value improves PM.[3] So, it acts like a compensation capacitor (network). To compensate multi-stage amplifiers, compensation capacitor is usually used to move dominant pole to lower frequency in order to achieve enough PM.

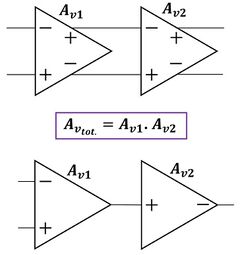

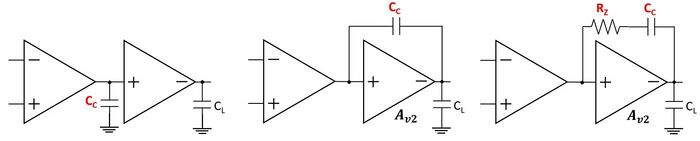

The following figure shows the block diagram of a two-stage amplifier in fully differential and single ended modes. In a two-stage amplifier, input stage can be a Telescopic or FC amplifier. For the second stage, common source amplifier with active load is a common choice. Since output resistance of the first stage is much greater than the second stage, dominant pole is at the output of the first stage. Without compensation, the amplifier is unstable or at least it does not have enough PM. It is important to mention that the load capacitance will be connected to the output of the second stage, which non-dominant pole happens there. Therefore, unlike single-stage amplifiers, increasing of capacitive load, will move non-dominant pole to lower frequency and will deteriorate PM.[3] Mesri et al. suggested two-stage amplifiers which behave like single-stage amplifiers, and amplifiers remains stable for larger values of capacitive loads.[6][7] To have proper behavior, we need to compensate two-stage or multi-stage amplifiers. The simplest way for compensation of two-stage amplifier, as shown in the left block diagram of the below figure, is to connect compensation capacitor at the output of the first stage, and move dominant pole to lower frequencies. But, realization of capacitor on silicon chip requires considerable area. The most common compensation method in two-stage amplifiers is Miller compensation (middle block diagram in the below figure.[2][3][8] In this method, a compensation capacitor is placed between input and output node of the second stage. In this case, the compensation capacitor will appear 1+|Av2| times greater at the output of the first stage, and will push the dominant pole as well as unity gain frequency to lower frequencies. Moreover, because of pole splitting effect, it will also move the non-dominant pole to higher frequencies. Therefore, it is a good candidate to make the amplifier stable. The main advantage of Miller compensation method, is to reduce size of the required compensation capacitor by a factor of 1+|Av2|. The issue raised from Miller compensation capacitor is introducing right-half plane (RHP) zero, which reduces PM. Hopefully, different methods have suggested to solve this issue. As an example, to cancel the effect of RHP zero, nulling resistor can be used in series with compensation capacitor (right block diagram of the below figure). Based on the resistor value, we can push RHP zero to higher frequency (in order to cancel its effect on PM), or to move it LHP (in order to improve PM), or even remove the first non-dominant pole to improve Bandwidth and PM. This method of compensation is recently used in amplifier design for potentiostat circuit.[11] Because of process variation, resistor value can change more than 10%, and therefore affects stability. Using current buffer or voltage buffer in series with compensation capacitor is another option to get better results.[2][3][8]

References

- ↑ 1.0 1.1 Razavi, Behzad (2013). Fundamentals of Microelectronics (2nd ed.). John Wiley & Sons. ISBN 9781118156322. https://www.safaribooksonline.com/library/view/fundamentals-of-microelectronics/9781118156322/. Retrieved 13 June 2018.

- ↑ 2.0 2.1 2.2 2.3 2.4 2.5 2.6 Sansen, Willy (2006). Analog Design Essentials. Springer. ISBN 978-0-387-25747-1. https://www.springer.com/it/book/9780387257464. Retrieved 13 June 2018.

- ↑ 3.00 3.01 3.02 3.03 3.04 3.05 3.06 3.07 3.08 3.09 Razavi, Behzad (2001). Design of Analog CMOS Integrated Circuits (1st ed.). McGraw-Hill Education. ISBN 978-0070529038.

- ↑ "Here's How Hard It Was to Move a 5MB IBM Hard Drive in 1956 (Note: Required a Forklift)". 2016-12-12. http://themindcircle.com/move-5mb-ibm-hard-drive-1956/. Retrieved 13 June 2018.

- ↑ "The best USB flash drives of 2018". https://www.techradar.com/news/best-usb-flash-drives. Retrieved 13 June 2018.

- ↑ 6.0 6.1 6.2 Mesri, Alireza; Mahdipour Pirbazari, Mahmoud; Hadidi, Khayrollah; Khoei, Abdollah (2015). "High gain two-stage amplifier with positive capacitive feedback compensation". IET Circuits, Devices & Systems 9 (3): 181–190. doi:10.1049/iet-cds.2014.0139. https://ieeexplore.ieee.org/stamp/stamp.jsp?tp=&arnumber=7103408&tag=1. Retrieved 13 June 2018.

- ↑ 7.0 7.1 Mesri, Alireza; Mahdipour Pirbazari, Mahmoud; Javidan, Javad (2015). "Analysis and design of a two-stage amplifier with enhanced performance". Microelectronics Journal 46 (12–A): 1304–1312. https://www.sciencedirect.com/science/article/pii/S0026269215002384. Retrieved 13 June 2018.

- ↑ 8.0 8.1 8.2 Leung, Ka Nang; K. T. Mok, Philip (2001). "Analysis of Multistage Amplifier–Frequency Compensation". IEEE Transactions on Circuits and Systems—I: Fundamental Theory and Applications 48 (9): 1041–1056. doi:10.1109/81.948432. https://ieeexplore.ieee.org/document/948432/. Retrieved 13 June 2018.

- ↑ S. Ghoreishizadeh, Sara; Taurino, Irene; De Micheli, Giovanni; Carrara, Sandro; Georgiou, Pantelis (2017). "A Differential Electrochemical Readout ASIC With Heterogeneous Integration of Bio-Nano Sensors for Amperometric Sensing". IEEE Transactions on Biomedical Circuits and Systems 11 (5): 1148–1159. doi:10.1109/TBCAS.2017.2733624. PMID 28885160. https://ieeexplore.ieee.org/document/8025834/. Retrieved 13 June 2018.

- ↑ A. Al Mamun, Khandaker; K. Islam, Syed; K. Hensley, Dale; McFarlane, Nicole (2016). "A Glucose Biosensor Using CMOS Potentiostat and Vertically Aligned Carbon Nanofibers". IEEE Transactions on Biomedical Circuits and Systems 10 (4): 807–816. doi:10.1109/TBCAS.2016.2557787. PMID 27337723. https://ieeexplore.ieee.org/document/7497511/. Retrieved 13 June 2018.

- ↑ 11.0 11.1 Giagkoulovits, Christos; Chong Cheah, Boon; A. Al-Rawhani, Mohammed; Accarino, Claudio; Busche, Christoph; P. Grant, James; R. S. Cumming, David (2018). "A 16 × 16 CMOS Amperometric Microelectrode Array for Simultaneous Electrochemical Measurements". IEEE Transactions on Circuits and Systems–I: Regular Papers PP (99): 1–11. doi:10.1109/TCSI.2018.2794502. https://ieeexplore.ieee.org/document/8283606/. Retrieved 13 June 2018.

- ↑ Mazhab Jafari, Hamed; Genov, Roman (2013). "Chopper-Stabilized Bidirectional Current Acquisition Circuits for Electrochemical Amperometric Biosensors". IEEE Transactions on Circuits and Systems—I: Regular Papers 60 (5): 1149–1157. doi:10.1109/TCSI.2013.2248771. https://ieeexplore.ieee.org/document/6504803/. Retrieved 13 June 2018.

- ↑ S. Assaad, Rida; Silva-Martinez, Jose (2009). "The Recycling Folded Cascode: A General Enhancement of the Folded Cascode Amplifier". Ieee Journal of Solid-State Circuits 44 (9): 2535–2542. doi:10.1109/JSSC.2009.2024819. https://ieeexplore.ieee.org/document/5226701/. Retrieved 13 June 2018.

- ↑ Nasri, Bayan; Wu, Ting; Alharbi, Abdullah; You, Kae-Dyi; Gupta, Mayank; P Sebastian, Sunit; Kiani, Roozbeh; Shahrjerdi, Davood (2017). "Hybrid CMOS-Graphene Sensor Array for Subsecond Dopamine Detection". IEEE Transactions on Biomedical Circuits and Systems 11 (6): 1192–1203. doi:10.1109/TBCAS.2017.2778048. PMID 29293417. PMC 5936076. https://ieeexplore.ieee.org/document/8187660/.

- ↑ Grasso, Alfio Dario; Palumbo, Gaetano; Salvatore, Pennisi (2015). "High-Performance Four-Stage CMOS OTA Suitable for Large Capacitive Loads". IEEE Transactions on Circuits and Systems—I: Regular Papers 62 (10): 2476–2484. doi:10.1109/TCSI.2015.2476298. https://ieeexplore.ieee.org/abstract/document/7277177/. Retrieved 14 June 2018.

- ↑ Cabrera-Bernal, Elena; Pennisi, Salvatore; Dario Grasso, Alfio; Torralba, Antonio; Gonzalez Carvajal, Ramón (2016). "0.7-V Three-Stage Class-AB CMOS Operational Transconductance Amplifier". IEEE Transactions on Circuits and Systems—I: Regular Papers 63 (11): 1807–1815. doi:10.1109/TCSI.2016.2597440. https://ieeexplore.ieee.org/abstract/document/7556409/. Retrieved 15 June 2018.

- ↑ Grasso, A.D.; Palumbo, G.; Pennisi, S. (2018). "Dual push-pull high-speed rail-to-rail CMOS buffer amplifier for flat-panel displays". IEEE Transactions on Circuits and Systems II: Express Briefs: 1. doi:10.1109/TCSII.2018.2817261. https://ieeexplore.ieee.org/abstract/document/8320304/. Retrieved 15 June 2018.