Engineering:Logarithmic resistor ladder

A logarithmic resistor ladder is an electronic circuit, composed of a series of resistors and switches, designed to create an attenuation from an input to an output signal, where the logarithm of the attenuation ratio is proportional to a binary number that represents the state of the switches.

The logarithmic behavior of the circuit is its main differentiator in comparison with digital-to-analog converters (DACs) in general, and traditional R-2R Ladder networks specifically. Logarithmic attenuation is desired in situations where a large dynamic range needs to be handled. The circuit described in this article is applied in audio devices, since humans perceive sound on a logarithmic scale.

Logarithmic input/output behavior

As in digital-to-analog converters, a binary number is applied to the ladder network, whose N bits are treated as representing an integer value:

where is 0 or 1 depending on the state of the ith switch.

For comparison, recall a conventional linear DAC or R-2R network produces an output voltage signal of:

where and are design constants and where typically is a constant reference voltage (or is a variable input voltage for a multiplying DAC.[1])

In contrast, the logarithmic ladder network discussed in this article creates a behavior as:

which can also be expressed as multiplied by some base raised to the power of the code value:

where

Circuit implementation

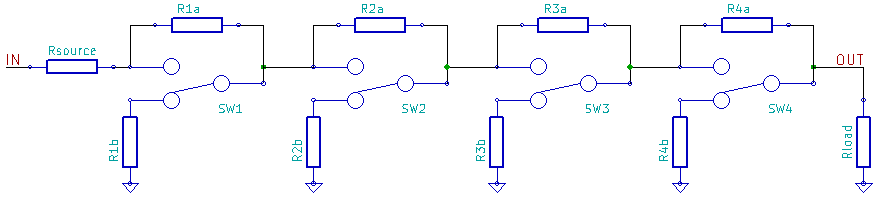

This example circuit is composed of 4 stages, numbered 1 to 4, and includes a source resistance Rsource and load resistance Rload.

Each stage i has a designed input-to-output voltage attenuation Ratioi as:

For logarithmic scaled attenuators, it is common practice to equivalently express their attenuation in decibels:

- for and

This reveals a basic property:

To show that this satisfies the overall intention:

The different stages 1 .. N should function independently of each other, as to obtain 2N different states with a composable behavior. To achieve an attenuation of each stage that is independent of its surrounding stages, either one of two design choices is to be implemented: constant input resistance or constant output resistance. Because the stages operate independently, they can be inserted in the chain in any order.

Constant input resistance

The input resistance of any stage shall be independent of its on/off switch position, and must be equal to Rload.

This leads to:

With these equations, all resistor values of the circuit diagram follow easily after choosing values for N, and Rload. (The value of Rsource does not influence the logarithmic behavior)

Constant output resistance

The output resistance of any stage shall be independent of its on/off switch position, and must be equal to Rsource.

This leads to:

Again, all resistor values of the circuit diagram follow easily after choosing values for N, and Rsource. (The value of Rload does not influence the logarithmic behavior).

For example, with a Rload of 1 kΩ, and 1 dB attenuation, the resistor values would be: Ra = 108.7 Ω, Rb = 8195.5 Ω.

The next step (2 dB) would use: Ra = 369.0 Ω, Rb = 1709.7 Ω.

Circuit variations

- The circuit as depicted above, can also be applied in reverse direction. That correspondingly reverses the role of constant-input and constant-output resistance equations.

- Since the stages do not significantly influence each other's attenuation, the stage order can be chosen arbitrarily. Such reordering can have a significant effect on the input resistance of the constant output resistance attenuator and vice versa.

Background

R-2R ladder networks used for linear digital-to-analog conversion are old (Resistor ladder § History mentions a 1953 article and a 1955 patent).

Multiplying DACs with logarithmic behavior were not known for a long time after that. An initial approach was to map the logarithmic code to a much longer code word, which could be applied to the classical (linear) R-2R based DAC. Lengthening the codeword is needed in that approach to achieve sufficient dynamic range. This approach was implemented in a device from Analog Devices Inc.,[2] protected through a 1981 patent filing.[3]

See also

References

- ↑ "Multiplying DACs, flexible building blocks". Analog Devices inc.. 2010. http://www.analog.com/static/imported-files/overviews/AnalogMultiplyingDACs.pdf. Retrieved 29 March 2012.

- ↑ "LOGDAC CMOS Logarithmic D/A Converter AD7118". Analog Devices Inc.. http://www.analog.com/media/en/technical-documentation/obsolete-data-sheets/1257410AD7118.pdf.

- ↑ Burton, David P., "Signal-controllable attenuator employing a digital-to-analog converter", US patent 4521764, issued 4 June 1985

External links

- Online calculator to configure logarithmic ladder networks

|