Engineering:Lookahead carry unit

A lookahead carry unit (LCU) is a logical unit in digital circuit design used to decrease calculation time in adder units and used in conjunction with carry look-ahead adders (CLAs).

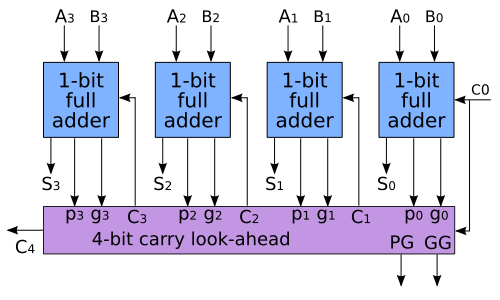

4-bit adder

A single 4-bit CLA is shown below:

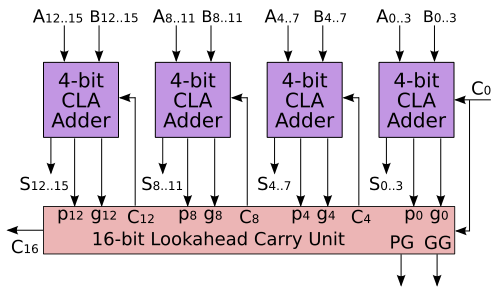

16-bit adder

By combining four 4-bit CLAs, a 16-bit adder can be created but additional logic is needed in the form of an LCU.

The LCU accepts the group propagate () and group generate () from each of the four CLAs. and have the following expressions for each CLA adder:[1]

The LCU then generates the carry input for each CLA.

Assume that is and is from the ith CLA then the output carry bits are

Substituting into , then into , then into yields the expanded equations:

corresponds to the carry input into the second CLA; to the third CLA; to the fourth CLA; and to overflow carry bit.

In addition, the LCU can calculate its own propagate and generate:

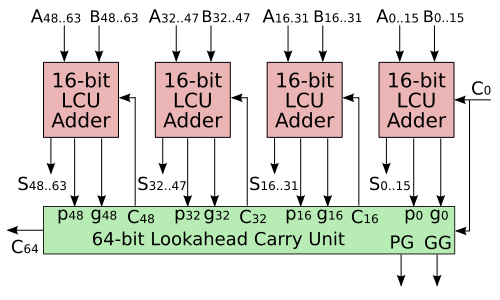

64-bit adder

By combining 4 CLAs and an LCU together creates a 16-bit adder. Four of these units can be combined to form a 64-bit adder. An additional (second-level) LCU is needed that accepts the propagate () and generate () from each LCU and the four carry outputs generated by the second-level LCU are fed into the first-level LCUs.

References

- ↑ "Carry Look Ahead Adder". Archived from the original on 2011-09-25. https://web.archive.org/web/20110925185302/http://www.seas.upenn.edu/~ese171/lab/CarryLookAhead/CarryLookAheadF01.html. Retrieved 2011-10-07.

- Katz, Randy (1994). Contemporary Logic Design. The Benjamin/Cummings Publishing Company. pp. 249–256. ISBN 0-8053-2703-7. https://archive.org/details/contemporarylogi00katz/page/249.

- Vahid, Frank (2006). Digital Design. John Wiley and Sons Publishers. pp. 296–316. ISBN 0-470-04437-3. https://archive.org/details/digitaldesign00vahi.

de:Paralleladdierer mit Übertragsvorausberechnung

|