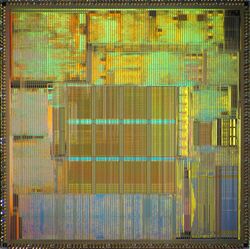

Engineering:TriMedia (mediaprocessor)

TriMedia is a family of very long instruction word media processors from NXP Semiconductors (formerly Philips Semiconductors). TriMedia is a Harvard architecture[citation needed] CPU that features many DSP and SIMD operations to efficiently process audio and video data streams. For TriMedia processor optimal performance can be achieved by only programming in C/C++ as opposed to most other VLIW/DSP processors which require assembly language programming to achieve optimal performance[citation needed]. High-level programmability of TriMedia relies on the large uniform register file and the orthogonal instruction set, in which RISC-like operations can be scheduled independently of each other in the VLIW issue slots. Furthermore, TriMedia processors boast advanced caches supporting unaligned accesses without performance penalty, hardware and software data/instruction prefetch, allocate-on-write-miss, as well as collapsed load operations combining a traditional load with a 2-taps filter function. TriMedia development has been supported by various research studies on hardware cache coherency, multithreading and diverse accelerators to build scalable shared memory multiprocessor systems.

Features

- 5 to 8 issue slots filled with up to 45 functional units

- 128 32-bit general purpose registers

- SIMD & DSP operations

- 32-bit IEEE 754 floating point operations

- 8/16/32/64 KB Instruction cache, 8/16/32/64/128 KB Data cache

- separate memory and peripheral bus interfaces

- up to 8 built-in timers

- up to 64 built-in vectored interrupts

- supported by an ANSI compliant C/C++ compiler toolchain

History

The first TriMedia was created in 1987 under the name LIFE-1 VLIW processor by Gerrit Slavenburg and Junien Labrousse. For the next several years LIFE was further matured internally in Philips under guidance of Gerrit Slavenburg, which resulted in 1996 in the introduction of the first Trimedia product: the TM1000 PCI Media Processor (introduced as TM-1 [1]). In 1998 the TM1100 and TM1300 (later renamed to PNX1300) products were introduced.[citation needed]

In 2000, Philips spun out its TriMedia business to TriMedia Technologies Inc. (TTI) which was a pure “IP vendor”. TTI tried unsuccessfully to create a 64 bit next generation TriMedia CPU architecture. This venture was ill-timed, as it was right at the start of the Dot-com recession. In 2003 what was left of TTI was re-absorbed within Philips.[2]

In 2002, the TM3260 CPU was released in the PNX1500 Media Processor SoC. This CPU was the first of a family of modular Trimedia CPU cores with standardized interfaces that can easily be integrated inside Audio/Video SoC's. The TM3260 has found use in other NXP products, e.g. the PNX8550 Home Entertainment Engine. In 2004 the super pipelined TM5250 CPU core was announced and won the Best Media Processor of 2003 [3] award from Microprocessor Report. This processor was made available in the PNX1700 Media Processor SoC.[4] These two CPU cores were designed by Jan-Willem van de Waerdt in close cooperation with Gerrit Slavenburg.[citation needed]

In 2005, the TM3270 was announced as a low-power H.264 capable incarnation of the TriMedia architecture (see external links to papers below), first released in the PNX4103 SoC.[5]

In 2006, Philips Semiconductors as a whole was spun off from Philips and was renamed to NXP.[6]

In 2009, the PNX1005 became available, using the latest TM3282 CPU core. This CPU is the first TriMedia to have 8 issue slots. It also adds more operations for H.264 and video optimization, data-cache pre-allocating and a bit-stream coprocessor for entropy en/de-coding. It is also the first TriMedia to have a real-time trace block.

In 2010, the TriMedia group at NXP was terminated.

Cores

| Core | year 1st

silicon |

ISA | Features | Cache (I/D) KB | frequency

(worst case) |

introduction technology |

|---|---|---|---|---|---|---|

| TM1000 | 1997 | TMA0 | 32/16 | 100 MHz | 500 nm | |

| TM1100 | 1998 | TMA1 | 32/16 | 133 MHz | 350 nm | |

| TM1300 | 1999 | TMA1 | 32/16 | 166 MHz | 250 nm | |

| TM3260 | 2002 | TMA2 | binary compatible with TM1300 | 64/16 | 250 MHz | 130 nm |

| TM5250 | 2004 | TMA3 | 128 KB L2 data cache,

allocate on write miss, hardware prefetching, super pipelined (high speed) |

64/16 | 450 MHz | 130 nm |

| TM2270 | 2006 | TMA3 | 96 GPRs (small area) | 32/16 | 290 MHz | 90 nm |

| TM3270/1 | 2006 | TMA4 + ASE | low power | 64/128

64/32 32/16 |

350 MHz | 90 nm |

| TM3282 | 2009 | TMA4 + ASE2 | 8-issue, pre-allocate, bit-stream coprocessor, real-time trace | 64/128 | 400 MHz | 90 nm |

| TM? | 2009 | TMA4 + ASE2? | 8-issue? | ?/? | 500 MHz | 45 nm[7] |

Products

The TriMedia cores were typically used in home, mobile and automotive products (see as an example Philips' Streamium networked multi-media products). They are used as deeply embedded CPUs in SoCs as well as general purpose DSPs. Some SoCs even have multiple TriMedia cores such as the PNX5100 that contains three TM3271 cores.[8]

With the growing complexity of SoC platforms, in subsequent years, the basic TriMedia CPU cores were also included in more highly integrated media processor SoC products, but these were launched under the Nexperia brand.

See also

- pSOS for TriMedia

References

- ↑ The Trimedia TM-1 PCI VLIW Media Processor

- ↑ Processor-core IP companies the hardest hit by semiconductor slump

- ↑ Processor Watch: Best Media Processor: TriMedia TM5250

- ↑ Processor Watch: Philips Debuts Media Processor

- ↑ Philips Nexperia Mobile Multimedia Processor PNX4103

- ↑ Forbes: NXP Hits The Ground Running (2006/09/01)

- ↑ Paper: Heterogeneous Multi-Core Platform for Consumer Multimedia Applications

- ↑ Product brief: NXP video back-end processor PNX5100

External links

- http://www.philips.com

- http://www.nxp.com

- Trident’s acquisition of NXP’s television systems and set-top box business lines

- paper: The TM3270 Media-Processor (pdf for IEEE members only)

- paper: The TM3270 Media-Processor (open to anyone)

- paper: The TM3270 Media-Processor Data Cache (pdf)

- paper: Motion Estimation Performance of the TM3270 Processor (pdf)

- EEMBC Consumer benchmark scores-- EEMBC, the Embedded Microprocessor Benchmark Consortium, is a non-profit corporation

- Press release for TM3282 EEMBC benchmark scores

- BDTi Video encoder and decoder benchmarks