Engineering:Tunnel field-effect transistor

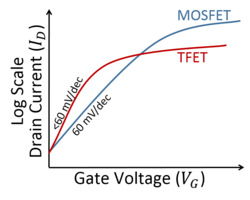

The tunnel field-effect transistor (TFET) is an experimental type of transistor. Even though its structure is very similar to a metal–oxide–semiconductor field-effect transistor (MOSFET), the fundamental switching mechanism differs, making this device a promising candidate for low power electronics. TFETs switch by modulating quantum tunneling through a barrier instead of modulating thermionic emission over a barrier as in traditional MOSFETs. Because of this, TFETs are not limited by the thermal Maxwell–Boltzmann tail of carriers, which limits MOSFET drain current subthreshold swing to about 60 mV/decade of current at room temperature. TFET studies can be traced back to Stuetzer who in 1952 published first investigations of a transistor containing the basic elements of the TFET, a gated p-n junction. The reported surface conductivity control was, however, not related to tunneling.[1] The first TFET was reported in 1965.[2] Joerg Appenzeller and his colleagues at IBM were the first to demonstrate that current swings below the MOSFET’s 60-mV-per-decade limit were possible. In 2004, they reported they had created a tunnel transistor with a carbon nanotube channel and a subthreshold swing of just 40 mV per decade.[3] Theoretical work has indicated that significant power savings can be obtained by using low-voltage TFETs in place of MOSFETs in logic circuits.[4]

In classical MOSFET devices, the 60 mV/decade is a fundamental limit to power scaling. The ratio between on-current and the off-current (especially the subthreshold leakage — one major contributor of power consumption) is given by the ratio between the threshold voltage and the subthreshold slope, e.g.:

- [math]\displaystyle{ n = 60 \,\, \mathrm{mV/decade}; \,\,\, V_{\rm th} = 300 \,\, \mathrm{mV} \,\, \rightarrow \,\, I_{\rm on}/I_{\rm off} = V_{\rm th}/n = 5 \,\, \mathrm{decades} = 100\,000 }[/math]

The transistor speed is proportional to the on-current: The higher the on-current, the faster a transistor will be able to charge its fan-out (consecutive capacitive load). For a given transistor speed and a maximum acceptable subthreshold leakage, the subthreshold slope thus defines a certain minimal threshold voltage. Reducing the threshold voltage is an essential part for the idea of constant field scaling. Since 2003, the major technology developers got almost stuck in threshold voltage scaling and thus could also not scale supply voltage (which due to technical reasons has to be at least 3 times the threshold voltage for high performance devices). As a consequence, the processor speed did not develop as fast as before 2003 (see Beyond CMOS). The advent of a mass-producible TFET device with a slope far below 60 mV/decade will enable the industry to continue the scaling trends from the 1990s, where processor frequency doubled each 3 years.

Structure

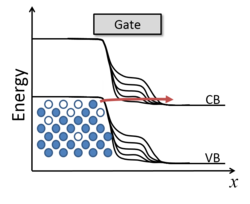

The basic TFET structure is similar to a MOSFET except that the source and drain terminals of a TFET are doped of opposite types (see figure). A common TFET device structure consists of a P-I-N (p-type, intrinsic, n-type) junction, in which the electrostatic potential of the intrinsic region is controlled by a gate terminal.

Device operation

The device is operated by applying gate bias so that electron accumulation occurs in the intrinsic region for an n-type TFET. At sufficient gate bias, band-to-band tunneling (BTBT) occurs when the conduction band of the intrinsic region aligns with the valence band of the P region. Electrons from the valence band of the p-type region tunnel into the conduction band of the intrinsic region and current can flow across the device.[5] As the gate bias is reduced, the bands become misaligned and current can no longer flow.

Prototype devices

A group at IBM were the first to demonstrate that current swings below the MOSFET’s 60-mV-per-decade limit were possible. In 2004, they reported a tunnel transistor with a carbon nanotube channel and a subthreshold swing of just 40 mV per decade.[6]

By 2010, many TFETs have been fabricated in different material systems,[4] but none has yet been able to demonstrate steep subthreshold slope at drive currents required for mainstream applications. In IEDM' 2016, a group from Lund University demonstrated a vertical nanowire InAs/GaAsSb/GaSb TFET,[7] which exhibits a subthreshold swing of 48 mV/decade, a on-current of 10.6 μA/μm for off-current of 1 nA/μm at a supply voltage of 0.3 V, showing the potential of outperforming Si MOSFETs at a supply voltage lower than 0.3 V.

Theory and simulations

Double-gate thin-body quantum well-to-quantum well TFET structures have been proposed to overcome some challenges associated with the lateral TFET structure, such as its requirement for ultra sharp doping profiles; however, such devices may be plagued by gate leakage due to large vertical fields in the device structure.[8]

Simulations in 2013 showed that TFETs using InAs-GaSb may have a subthreshold swing of 33 mV/decade under ideal conditions.[9]

The use of van der Waals heterostructures for TFETs were proposed in 2016.[10]

See also

References

- ↑ Stuetzer, O.M. (1952). "Junction fieldistors". Proceedings of the IRE 40 (11): 1377–81. doi:10.1109/JRPROC.1952.273965.

- ↑ Hofstein, S.R.; Warfield, G. (1965). "The insulated gate tunnel junction triode". IEEE Transactions on Electron Devices 12 (2): 66–76. doi:10.1109/T-ED.1965.15455. Bibcode: 1965ITED...12...66H.

- ↑ Appenzeller, J. (2004-01-01). "Band-to-Band Tunneling in Carbon Nanotube Field-Effect Transistors". Physical Review Letters 93 (19): 196805. doi:10.1103/PhysRevLett.93.196805. PMID 15600865. Bibcode: 2004PhRvL..93s6805A.

- ↑ 4.0 4.1 Seabaugh, A. C.; Zhang, Q. (2010). "Low-Voltage Tunnel Transistors for Beyond CMOS Logic". Proceedings of the IEEE 98 (12): 2095–2110. doi:10.1109/JPROC.2010.2070470.

- ↑ Zhang, Lining, ed (2016) (in en). Tunneling Field Effect Transistor Technology. Cham: Springer International Publishing. doi:10.1007/978-3-319-31653-6. ISBN 978-3-319-31651-2. http://link.springer.com/10.1007/978-3-319-31653-6.

- ↑ Seabaugh (September 2013). "The Tunneling Transistor". IEEE Spectrum. IEEE. https://spectrum.ieee.org/semiconductors/devices/the-tunneling-transistor.

- ↑ Memisevic, E.; Svensson, J.; Hellenbrand, M.; Lind, E.; Wernersson, L.-E. (2016). "Vertical InAs/GaAsSb/GaSb tunneling field-effect transistor on Si with S = 48 mV/Decade and Ion = 10 μA/μm for Ioff = 1 nA/μm at Vds = 0.3 V". 2016 IEEE International Electron Devices Meeting (IEDM). pp. 19.1.1–4. doi:10.1109/IEDM.2016.7838450. ISBN 978-1-5090-3902-9. https://ieeexplore.ieee.org/document/7838450.

- ↑ Teherani, J. T.; Agarwal, S.; Yablonovitch, E.; Hoyt, J. L.; Antoniadis, D. A. (2013). "Impact of Quantization Energy and Gate Leakage in Bilayer Tunneling Transistors". IEEE Electron Device Letters 34 (2): 298. doi:10.1109/LED.2012.2229458. Bibcode: 2013IEDL...34..298T.

- ↑ Huang, David; Fang, Hui; Javey, Ali (2013). "Device Simulation of Tunnel Field Effect Transistor (TFET)". University of California. https://e3s-center.berkeley.edu/wp-content/uploads/2017/07/Huang_David.pdf.

- ↑ Cao, Jiang; Logoteta, Demetrio; Ozkaya, Sibel; Biel, Blanca; Cresti, Alessandro; Pala, Marco G.; Esseni, David (2016). "Operation and Design of van der Waals Tunnel Transistors: A 3-D Quantum Transport Study". IEEE Transactions on Electron Devices 63 (11): 4388–94. doi:10.1109/TED.2016.2605144. Bibcode: 2016ITED...63.4388C.

|