Engineering:Frequency divider

A frequency divider, also called a clock divider or scaler or prescaler, is a circuit that takes an input signal of a frequency, , and generates an output signal of a frequency:

where is an integer. Phase-locked loop frequency synthesizers make use of frequency dividers to generate a frequency that is a multiple of a reference frequency. Frequency dividers can be implemented for both analog and digital applications.

Analog

Analog frequency dividers are less common and used only at very high frequencies. Digital dividers implemented in modern IC technologies can work up to tens of GHz.[citation needed]

Regenerative

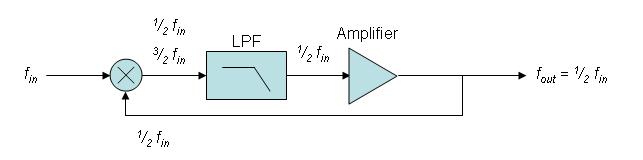

A regenerative frequency divider, also known as a Miller frequency divider,[1] mixes the input signal with the feedback signal from the mixer.

The feedback signal is . This produces sum and difference frequencies , at the output of the mixer. A low pass filter removes the higher frequency, and the frequency is amplified and fed back into the mixer.

Injection-locked

A free-running oscillator which has a small amount of a higher-frequency signal fed to it, will tend to oscillate in step with the input signal. Such frequency dividers were essential in the development of television.

It operates similarly to an injection locked oscillator. In an injection-locked frequency divider, the frequency of the input signal is a multiple (or fraction) of the free-running frequency of the oscillator. While these frequency dividers tend to be lower power than broadband static (or flip-flop-based) frequency dividers, the drawback is their low locking range. The ILFD locking range is inversely proportional to the quality factor (Q) of the oscillator tank. In integrated circuit designs, this makes an ILFD sensitive to process variations. Care must be taken to ensure the tuning range of the driving circuit (for example, a voltage-controlled oscillator) must fall within the input locking range of the ILFD.

Digital

For power-of-2 integer division, a simple binary counter can be used, clocked by the input signal. The least-significant output bit alternates at 1/2 the rate of the input clock, the next bit at 1/4 the rate, the third bit at 1/8 the rate, etc. An arrangement of flipflops is a classic method for integer-n division. Such division is frequency and phase coherent to the source over environmental variations, including temperature. The easiest configuration is a series where each flip-flop is a divide-by-2. For a series of three of these, such a system would be a divide-by-8. By adding additional logic gates to the chain of flip-flops, other division ratios can be obtained. Integrated circuit logic families can provide a single-chip solution for some common division ratios.

Another popular circuit to divide a digital signal by an even integer multiple is a Johnson counter. This is a type of shift register network that is clocked by the input signal. The last register's complemented output is fed back to the first register's input. The output signal is derived from one or more of the register outputs. For example, a divide-by-6 divider can be constructed with a 3-register Johnson counter. The six valid values of the counter are 000, 100, 110, 111, 011, and 001. This pattern repeats each time the input signal clocks the network. The output of each register is an f/6 square wave with 120° of phase shift between registers. Additional registers can be added to provide additional integer divisors.

Mixed signal

(Classification: asynchronous sequential logic)

An arrangement of D flip-flops is a classic method for integer-n division. Such division is frequency and phase coherent to the source over environmental variations, including temperature. The easiest configuration is a series where each D flip-flop is a divide-by-2. For a series of three of these, such a system would be a divide-by-8. More complicated configurations have been found that generate odd factors, such as a divide-by-5. Standard, classic logic chips that implement this or similar frequency division functions include the 7456, 7457, 74292, and 74294. (see list of 7400 series and list of 4000 series logic chips)

Fractional-N synthesis

A fractional-n frequency synthesizer can be constructed using two integer dividers, a divide-by-N, and a divide-by-(N + 1) frequency divider. With a modulus controller, N is toggled between the two values so that the VCO alternates between one locked frequency and the other. The VCO stabilizes at a frequency that is the time average of the two locked frequencies. By varying the percentage of time the frequency divider spends at the two divider values, the frequency of the locked VCO can be selected with very fine granularity.

Delta-sigma

If the sequence of divide by N and divide by (N + 1) is periodic, spurious signals appear at the VCO output in addition to the desired frequency. Delta-sigma fractional-n dividers overcome this problem by randomizing the selection of N and (N + 1) while maintaining the time-averaged ratios.

See also

References

- ↑ R. L. Miller (1939). "Fractional Frequency Generators Utilizing Regenerative Modulation". Proceedings of the IRE 27 (7): 446–457. doi:10.1109/JRPROC.1939.228513.

External links

- Digital frequency dividers

- Divide by 2, and asynchronous 2N Ripple Counter dividers - Electronics Tutorials

- Synchronous divide by 3, 6, 9, 12 with 50% duty cycle output - ON Semiconductor

- Synchronous divide by 3 or 5 with 50% duty cycle output, and divide by 1.5 & 2.5 circuits - Xilinx

- Divide by N-0.5 using 74x161 counters - Whitepaper

|