Engineering:GAL22V10

| Design firm | Lattice Semiconductor |

|---|---|

| Type | Series of programmable-logic devices |

(same as GAL22V10)

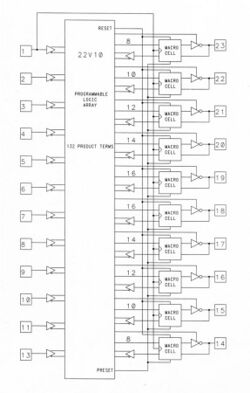

The GAL22V10 is a series of programmable-logic devices from Lattice Semiconductor, implemented as CMOS-based generic array logic ICs, and available in dual inline packages or plastic leaded chip carriers. It is an example of a standard production GAL (General Array Logic) device that is often used in educational settings as a basic programmable-logic device.[1][2][3] In combinatorial mode, it is conceptually a group of programmable AND-OR-invert (AOI) (AND-NOR) gates or AND-OR gates.

Specifications

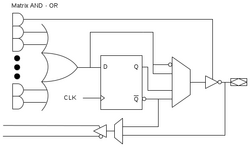

The GAL22V10 has 12 input pins, and 10 pins that can be configured as either inputs or outputs, and exists in various switching speeds, from 25 to 4 ns.[1][2][4] Each output is driven by an output-logic macrocell (OLMC), with an output-enable product term, and a variable number of product terms, ranging from eight to sixteen. Each OLMC may be set to output as inverting or non-inverting, and be placed into either registered or combinatorial mode. In registered mode, each macrocell actively uses a D-flip-flop to hold a state under control of the data input from the logic portion of the macrocell and the rising edge of the clock signal, while in combinatorial mode the flip-flop is removed from the macrocell and the outputs are driven directly by the logic. In the latter mode, the pin may also dynamically switch between input and output based on the product term. In either mode the pin value is fed back into the array as a product term. Combinations are set using an E2PROM.[3] The output registers can be preloaded into a potentially invalid state for testing by a GAL22V10 programmer. Inputs and outputs include active pull-ups and are transistor-transistor logic compatible due to high-impedance buffers.[5]

A user electronic signature section is included for details such as user ID codes, revision IDs, or asset tagging on official Lattice Semiconductor units, as well as a static ES section for compatibility with non-Lattice Semiconductor GAL22V10 units. In addition, a security cell is included which, when set, disallows the retrieval of the array logic from the chip, until a new set of logic is set.

Latch-up protection is implemented using n-pullups and a charge pump in the official Lattice Semiconductor models.

Availability

The GAL22V10D had been discontinued by Lattice Semiconductor as of June 2010 with the last shipment in June 2011. No pin-compatible replacements have been offered or recommended by Lattice.[6]

Multiple variations of the Microchip / Atmel ATF22V10 are pin-compatible replacements, and available in PDIP, SOIC, PLCC, TSSOP packages.

Related parts

The GAL16V8 and GAL20V8 are similar in concept to the GAL22V10, but have fewer I/O pins in smaller packages.

References

- ↑ 1.0 1.1 Foltz, Heinrich. "Supplemental Notes: GAL22V10 Programming". Electrical Engineering Laboratory I/II. University of Texas, Pan-American. http://faculty.utpa.edu/hfoltz/.../LAB1_Extra_GAL22V10_Programming.pdf. Retrieved 12 January 2014.

- ↑ 2.0 2.1 Reeder, Nick. "Programming a GAL22V10". EET1131 Digital Electronics. Sinclair Community College. Archived from the original on 20 February 2014. https://web.archive.org/web/20140220060159/http://people.sinclair.edu/nickreeder/eet1131/programmingGAL.htm. Retrieved 12 December 2013.

- ↑ 3.0 3.1 Dueck, Robert K. (2005). Digital design with CPLD applications and VHDL (2nd ed.). Clifton Park, N.Y.; [Canada]: Thomson/Delmar Learning. pp. 467–469. ISBN 1401840302.

- ↑ Wirth, N.. "The Programmable Logic Device ispGAL22V10". Institute of Computer Systems, Swiss Federal Institute of Technology, Zurich. http://www.cs.inf.ethz.ch/lola/gal22v10/. Retrieved 12 January 2014.

- ↑ "GAL22V10 Datasheet". Massachusetts Institute of Technology. http://web.mit.edu/6.115/www/document/gal22v10.pdf. Retrieved 6 December 2015.

- ↑ "PCN09I-10". Lattice Semiconductor. http://www.latticesemi.com/dynamic/view_document.cfm?document_id=37118. Retrieved 13 December 2013.

Further reading

- Historical books

- Programmable Logic Designer's Guide; Roger Alford; Sams Publishing; 1989; ISBN 0-672-22575-1. (archive)

- PAL Programmable Logic Handbook; 4ed; Monolithic Memories; 407 pages; 1985. (archive)

- PEEL Software and Applications Handbook; International CMOS Technology (ICT); 138 pages; 1989. (archive)

- (also, see design guide sections of databooks below)

- Historical Lattice documents

- Introduction to GAL Device Architectures; 15 pages; 1998.

- Lattice GAL22V10 datasheet; 29 pages; 1998.

- Lattice GAL16V8 datasheet; 22 pages; 2001.

- Historical AMD documents

- AMD PALCE16V8H Datasheet and Design Guide; 61 pages; 1989.

- AMD PAL Databook and Design Guide; 764 pages; 1993.

- Historical National documents

- National Programmable Logic Devices Databook and Design Guide; 502 pages; 1990.

- Microchip/Atmel documents (modern lower-power parts that are still being manufactured)

- Microchip ATF22V10B, ATF22V10C, ATF22V10CQ, ATF22V10CQZ datasheets.

- Microchip ATF16V8B, ATF16V8BQL, ATF16V8C, ATF16V8CZ datasheets.

External links

- GALasm - open-source GAL assembler.

- Galette - open-source GAL assembler.

- Afterburner - open-source GAL hardware programmer.

|