Engineering:High-κ dielectric

In the semiconductor industry, the term high-κ dielectric refers to a material with a high dielectric constant (κ, kappa), as compared to silicon dioxide. High-κ dielectrics are used in semiconductor manufacturing processes where they are usually used to replace a silicon dioxide gate dielectric or another dielectric layer of a device. The implementation of high-κ gate dielectrics is one of several strategies developed to allow further miniaturization of microelectronic components, colloquially referred to as extending Moore's Law.

Sometimes these materials are called "high-k" (pronounced "high kay"), instead of "high-κ" (high kappa).

Need for high-κ materials

Silicon dioxide (SiO

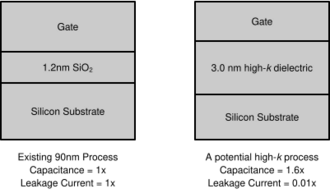

2) has been used as a gate oxide material for decades. As metal–oxide–semiconductor field-effect transistors (MOSFETs) have decreased in size, the thickness of the silicon dioxide gate dielectric has steadily decreased to increase the gate capacitance [inconsistent] (per unit area) and thereby drive current (per device width), raising device performance. As the thickness scales below 2 nm, leakage currents due to tunneling increase drastically, leading to high power consumption and reduced device reliability. Replacing the silicon dioxide gate dielectric with a high-κ material allows decreasing gate thickness[inconsistent] thus increasing gate capacitance without the associated leakage effects.

First principles

The gate oxide in a MOSFET can be modeled as a parallel plate capacitor. Ignoring quantum mechanical and depletion effects from the Si substrate and gate, the capacitance C of this parallel plate capacitor is given by

where

- A is the capacitor area

- κ is the relative dielectric constant of the material (3.9 for silicon dioxide)

- ε0 is the permittivity of free space

- t is the thickness of the capacitor oxide insulator

Since leakage limitation constrains further reduction of t, an alternative method to increase gate capacitance is to alter κ by replacing silicon dioxide with a high-κ material. In such a scenario, a thicker gate oxide layer might be used which can reduce the leakage current flowing through the structure as well as improving the gate dielectric reliability.

Gate capacitance impact on drive current

The drain current ID for a MOSFET can be written (using the gradual channel approximation) as

where

- W is the width of the transistor channel

- L is the channel length

- μ is the channel carrier mobility (assumed constant here)

- Cinv is the capacitance density associated with the gate dielectric when the underlying channel is in the inverted state

- VG is the voltage applied to the transistor gate

- Vth is the threshold voltage

The term VG − Vth is limited in range due to reliability and room temperature operation constraints, since a too large VG would create an undesirable, high electric field across the oxide. Furthermore, Vth cannot easily be reduced below about 200 mV, because leakage currents due to increased oxide leakage (that is, assuming high-κ dielectrics are not available) and subthreshold conduction raise stand-by power consumption to unacceptable levels. (See the industry roadmap,[1] which limits threshold to 200 mV, and Roy et al. [2]). Thus, according to this simplified list of factors, an increased ID,sat requires a reduction in the channel length or an increase in the gate dielectric capacitance.

Materials and considerations

Replacing the silicon dioxide gate dielectric with another material adds complexity to the manufacturing process. Silicon dioxide can be formed by oxidizing the underlying silicon, ensuring a uniform, conformal oxide and high interface quality. As a consequence, development efforts have focused on finding a material with a requisitely high dielectric constant that can be easily integrated into a manufacturing process. Other key considerations include band alignment to silicon (which may alter leakage current), film morphology, thermal stability, maintenance of a high mobility of charge carriers in the channel and minimization of electrical defects in the film/interface. Materials which have received considerable attention are hafnium silicate, zirconium silicate, hafnium dioxide and zirconium dioxide, typically deposited using atomic layer deposition.

It is expected that defect states in the high-κ dielectric can influence its electrical properties. Defect states can be measured for example by using zero-bias thermally stimulated current, zero-temperature-gradient zero-bias thermally stimulated current spectroscopy,[3][4] or inelastic electron tunneling spectroscopy (IETS).

Use in industry

Industry has employed oxynitride gate dielectrics since the 1990s, wherein a conventionally formed silicon oxide dielectric is infused with a small amount of nitrogen. The nitride content subtly raises the dielectric constant and is thought to offer other advantages, such as resistance against dopant diffusion through the gate dielectric.

In 2000, Gurtej Singh Sandhu and Trung T. Doan of Micron Technology initiated the development of atomic layer deposition high-κ films for DRAM memory devices. This helped drive cost-effective implementation of semiconductor memory, starting with 90-nm node DRAM.[5][6]

In early 2007, Intel announced the deployment of hafnium-based high-κ dielectrics in conjunction with a metallic gate for components built on 45 nanometer technologies, and has shipped it in the 2007 processor series codenamed Penryn.[7][8] At the same time, IBM announced plans to transition to high-κ materials, also hafnium-based, for some products in 2008. While not identified, the most likely dielectric used in such applications are some form of nitrided hafnium silicates (HfSiON). HfO

2 and HfSiO are susceptible to crystallization during dopant activation annealing. NEC Electronics has also announced the use of a HfSiON dielectric in their 55 nm UltimateLowPower technology.[9] However, even HfSiON is susceptible to trap-related leakage currents, which tend to increase with stress over device lifetime. This leakage effect becomes more severe as hafnium concentration increases. There is no guarantee, however, that hafnium will serve as a de facto basis for future high-κ dielectrics. The 2006 ITRS roadmap predicted the implementation of high-κ materials to be commonplace in the industry by 2010.

See also

References

- ↑ "Process Integration, Devices, and Structures". International Technology Roadmap for Semiconductors: 2006 Update. http://www.itrs.net/Links/2006Update/FinalToPost/04_PIDS2006Update.pdf.

- ↑ Kaushik Roy, Kiat Seng Yeo (2004). Low Voltage, Low Power VLSI Subsystems. McGraw-Hill Professional. pp. Fig. 2.1, p. 44. ISBN 978-0-07-143786-8. https://books.google.com/books?id=jXm4pNxCSCYC&q=subthreshold+mosfet+%22static+power%22.

- ↑ Lau, W. S.; Zhong, L.; Lee, Allen; See, C. H.; Han, Taejoon; Sandler, N. P.; Chong, T. C. (1997). "Detection of defect states responsible for leakage current in ultrathin tantalum pentoxide (Ta[sub 2]O[sub 5]) films by zero-bias thermally stimulated current spectroscopy". Applied Physics Letters 71 (4): 500. doi:10.1063/1.119590. Bibcode: 1997ApPhL..71..500L.

- ↑ Lau, W. S.; Wong, K. F.; Han, Taejoon; Sandler, Nathan P. (2006). "Application of zero-temperature-gradient zero-bias thermally stimulated current spectroscopy to ultrathin high-dielectric-constant insulator film characterization". Applied Physics Letters 88 (17): 172906. doi:10.1063/1.2199590. Bibcode: 2006ApPhL..88q2906L.

- ↑ "IEEE Andrew S. Grove Award Recipients". Institute of Electrical and Electronics Engineers. https://www.ieee.org/about/awards/bios/grove-recipients.html.

- ↑ Sandhu, Gurtej; Doan, Trung T. (22 August 2001). "Atomic layer doping apparatus and method". https://patents.google.com/patent/WO2002038841A3.

- ↑ "Intel 45nm High-k Silicon Technology Page". Intel.com. http://www.intel.com/technology/architecture-silicon/45nm-core2/index.htm.

- ↑ "IEEE Spectrum: The High-k Solution". http://www.spectrum.ieee.org/oct07/5553.

- ↑ "UltimateLowPower Technology|Advanced Process Technology|Technology|NEC Electronics". Necel.com. http://www.necel.com/process/en/lowpower_overview.html.

Further reading

- Review article by Wilk et al. in the Journal of Applied Physics

- Houssa, M. (Ed.) (2003) High-k Dielectrics Institute of Physics ISBN 0-7503-0906-7 CRC Press Online

- Huff, H.R., Gilmer, D.C. (Ed.) (2005) High Dielectric Constant Materials : VLSI MOSFET applications Springer ISBN 3-540-21081-4

- Demkov, A.A, Navrotsky, A., (Ed.) (2005) Materials Fundamentals of Gate Dielectrics Springer ISBN 1-4020-3077-0

- "High dielectric constant gate oxides for metal oxide Si transistors" Robertson, J. (Rep. Prog. Phys. 69 327-396 2006) Institute Physics Publishing doi:10.1088/0034-4885/69/2/R02 High dielectric constant gate oxides]

- Media coverage of March, 2007 Intel/IBM announcements BBC NEWS|Technology|Chips push through nano-barrier, NY Times Article (1/27/07)

- Gusev, E. P. (Ed.) (2006) "Defects in High-k Gate Dielectric Stacks: Nano-Electronic Semiconductor Devices", Springer ISBN 1-4020-4366-X