Engineering:Rigel (microprocessor)

Rigel was a microprocessor chip set developed and fabricated by Digital Equipment Corporation (DEC) that implemented the VAX instruction set architecture (ISA). It was introduced on 11 July 1989 with the introduction of the VAX 6000 Model 400, the first system to feature the chip set. Rigel was also used in the VAX 4000 Model 300 and VAXstation 3100 Model 76. Production Rigel CPUs were rated at 35 to 43 MHz.

The Rigel chipset consisted of several devices:

- REX520 central processing unit (also known as the DC520 or "P-chip")

- DC523 floating-point unit (codenamed KIWI or "F-chip" during development)

- DC592 cache controller (codenamed COW or "C-chip" during development)

- DC521 clock chip

In addition, two further devices implemented the VAX vector processor option; these comprised the DC555 Vector Register set chip (VERSE) and the DC556 Vector Data Path chip (FAVOR).

Support chips for Rigel-based systems included the RSSC (Rigel System Support Chip) and Ghidra, the VAX 4000 system interface chip.

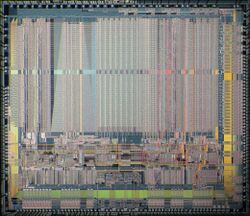

REX520

The Rigel architecture was based on the VAX 8800 processor. It has a six-stage microinstruction pipeline and 64-entry fully associative translation look-aside buffer. The Rigel chip set supported an optional vector processor and the REX520 decoded any vector instructions and passed on to the vector interface (VC) chip by the REX520.

The REX520 has a 2 KB unified primary cache, configurable as an instruction cache and an external 128 KB secondary cache (backup cache) implemented with CMOS static random access memory (SRAM) chips. The REX520 has an external cache because the VAX 8800's 64 KB primary cache could not be integrated on the same die. The backup cache controller was located on the VC chip.

The REX520 consisted of 320,000 transistors, of which 140,000 are for logic and 180,000 for memory. The die measures 12 mm by 12 mm (144 mm²). It was packaged in a 224-lead ceramic leaded package.

Fabrication

The chip set was fabricated by DEC in their second-generation complementary metal–oxide–semiconductor (CMOS) process, CMOS-2. The process had a 1.5 µm minimum feature size and two levels of aluminium interconnect.

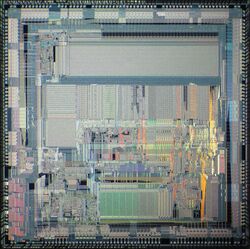

Mariah

Mariah was a revised version of the Rigel chip set fabricated by DEC in their 1 µm CMOS-3 process, with higher clock frequencies between 55 and 71 MHz. The Mariah CPU, FPU and cache controller were designated DC595, DC596 and DC597 respectively. Enhancements over Rigel included a 4 kB first-level cache and 32-bit physical memory addressing in the Mariah CPU, and write-back caching implemented in the cache controller chip. Mariah was used in the VAX 6000 Model 500, MicroVAX 3100 Model 80 and VAXstation 4000 Model 60.

References

- "Rigel" at The Computer History Simulation Project

- "Mariah" at The Computer History Simulation Project

- K.M.I. - the site

- Durdan, W. Hugh et al. (1990). "An Overview of the VAX 6000 Model 400 Chip Set". Digital Technical Journal, Volume 2, Number 2, 1990. pp. 36–51.

- Slater, Debra L. et al. (1990). "Vector Processing on the VAXvector 6000 Model 400". Digital Technical Journal, Volume 2, Number 2, 1990. pp. 11–26.

|