Engineering:Simple Bus Architecture

The Simple Bus Architecture[1] (SBA) is a form of computer architecture. It is made up software tools and intellectual property cores (IP core) interconnected by buses using simple and clear rules, that allow the implementation of an embedded system (SoC). Basic templates are provided to accelerate design. The VHDL code that implements this architecture is portable.

The SBA allows to accelerate the development of reconfigurable virtual instrumentation [2] systems. Science and engineering are based on measurements and comparisons, and each field requires a set of both standard and specialised (ad hoc) instruments to make these measurements. With the advent of powerful, low-cost, state-of-the-art field-programmable gate arrays (FPGAs), it is easier to provide virtual, reconfigurable, on-demand instrumentation.

FPGAs have grown in size and sophistication over the years and are now used in markets as diverse as telecommunications, consumer electronics, industrial and medical, to name a few. Many FPGA vendors now include additional features in their devices, such as integrated processor cores, memory, high-speed input/output (I/O) interfaces, etc. These additional capabilities, along with their low cost per unit, have made FPGAs increasingly popular for digital signal processing (DSP) applications.[3] However, notwithstanding the above, arguably the most important feature of FPGAs that has led to their rapid rise in popularity and use is their 'field programmability' or reconfigurability. Other features that make FPGAs very attractive are their high cell density and high level of parallelism, making them an ideal choice for computationally intensive applications that can be parallelized.

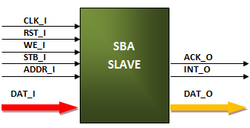

The Simple Bus Architecture, or SBA, allows different components or blocks to be interconnected to each other in a practical and simple way, allowing the user to optimise time when carrying out their projects. It also sacrifices the complexities of other implementations in order to easily introduce the SoC concept into the FPGA, so it has an inherent educational value. The SBA is intended to be a general purpose interface; as such, it defines the data exchange between standard IP core modules. It is divided into three main block types: master or system controller (SBA controller), slave cores and bus support cores (address decoder, bus adapters, clock generators, etc.).[4]

Components

Master core

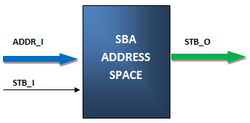

The master core is a finite-state machine (FSM) and performs basic data flow and processing, similar to a microprocessor, but with lower consumption of logic resources. It is the main block, as it is here that an address is assigned for each action to be performed. It is also in charge of deciding the order of these actions (it decides what to execute first and what to execute next). This addressing communicates directly with the Address Decoder.

Address decoder

Assigns each slave core a position in the address map and enables these cores through the chip enabler/selector.

Slave cores

Slaves are IP cores that provide some specific functionality, from data processing to serving as adapters between the SoC and devices external to the chip. In a system with multiple slaves, each slave has an established portion of the address map.

Wishbone

SBA is an application and a simplified version of the Wishbone[5] specification. SBA implements the minimum essential subset of the Wishbone signals interface. It can be connected with simple Wishbone IP cores. SBA defines three types of cores: masters, slaves, and auxiliaries. Several slave IP cores were developed following the SBA architecture, many to implement virtual instruments.

Applications

The SBA has been used to build differents ad hoc instruments like a wave generator,[6] curve tracer,[7] PWM controllers,[8] UAV instrumentation,[9] Bioelectrical signal processing [10] and many other electronic instruments.[11]

References

- ↑ "SBA - Simple Bus Architecture". Sba.accesus.com. http://sba.accesus.com. Retrieved 2014-05-15.

- ↑ "Reconfigurable Virtual Instrumentation Based on FPGA for Science and High-Education". https://www.researchgate.net/publication/305574433. Retrieved 2024-10-12.

- ↑ Maxfield, C. 2004. The Design Warrior's Guide to FPGAs: Devices, Tools and Flows. Elsevier 2004

- ↑ "Arquitectura de bus simple, un conjunto de herramientas para el desarrollo rápido y portable de sistemas en chip.". https://www.researchgate.net/publication/259823959.

- ↑ "SoC Interconnection: WISHBONE :: OpenCores". https://opencores.org/howto/wishbone.

- ↑ "Reconfigurable virtual instruments: Development of arbitrary waveform generator". https://www.researchgate.net/publication/258225127.

- ↑ Vega, J., & Risco, M. (2010). Desarrollo de un trazador de curvas como un caso de aplicación de instrumentos basados en instrumentación virtual reconfigurable. In Congreso de Microelectrónica Aplicada (pp. 93-98)

- ↑ "Development and implementation of the SBA interface for a 16 independent programmable channels PWM IP Core". doi:10.33017/RevECIPeru2010.0017/. https://doi.org/10.33017/RevECIPeru2010.0017/.

- ↑ "Implementation of a Guidance Determination System Guidance Determination System Using Sopc Design in a FPGA for Unmanned Aerial Vehicle Type Quadrotor". https://repositorio.utp.edu.pe/bitstream/handle/20.500.12867/123/0721114.pdf.

- ↑ Adeluyi, Olufemi; Risco-Castillo, Miguel A.; Liz Crespo, María; Cicuttin, Andres; Lee, Jeong-A. (January 15, 2020). "A Computerized Bioinspired Methodology for Lightweight and Reliable Neural Telemetry". Sensors 20 (22): 6461. doi:10.3390/s20226461. PMID 33198191. Bibcode: 2020Senso..20.6461A.

- ↑ Castillo, Miguel Alberto Risco (August 3, 2018). Diseño de instrumentos electrónicos mediante bloques de lógica reconfigurable y herramientas libres. doi:10.18687/laccei2018.1.1.374. ISBN 978-0-9993443-1-6. https://laccei.org/LACCEI2018-Lima/meta/FP374.html.

|