Tile processor

This article has multiple issues. Please help improve it or discuss these issues on the talk page. (Learn how and when to remove these template messages)

(Learn how and when to remove this template message)

|

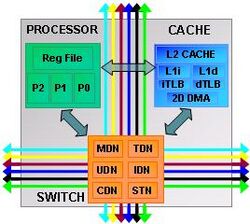

Tile processors[1] for computer hardware, are multi-core or manycore chips that contain one-dimensional, or more commonly, two-dimensional arrays of identical tiles. Each tile comprises a compute unit (or a processing engine or CPU), caches and a switch. Conceptually, a tile is similar to a traditional CPU core (a compute unit with caches), but with an integrated switch that connects it to the on-chip network.

In a typical Tile Processor configuration, the switches in each of the tiles are connected to each other using one or more mesh networks.[2] The Tilera TILEPro64, for example, contains 64 tiles. Each of the tiles comprises a CPU, L1 and L2 caches, and switches for several mesh networks.

Other processors in a tile configuration include SEAforth24, Kilocore KC256, XMOS xCORE microcontrollers, and some massively parallel processor arrays.

References

- ↑ The Tile Processor™ architecture: Embedded multicore for networking and digital multimedia - IEEE Conference Publication. August 2007. pp. 1–12. doi:10.1109/HOTCHIPS.2007.7482495.

- ↑ Wentzlaff, David (September 15, 2007). "On-Chip Interconnection Architecture of the Tile Processor". IEEE Micro. http://www.princeton.edu/~wentzlaf/documents/Wentzlaff.2007.IEEE_Micro.Tilera.pdf. doi:10.1109/MM.2007.89

|