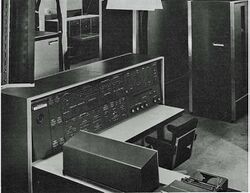

UNIVAC LARC

The UNIVAC LARC, short for the Livermore Advanced Research Computer, is a mainframe computer designed to a requirement published by Edward Teller in order to run hydrodynamic simulations for nuclear weapon design. It was one of the earliest supercomputers.[1] It used solid-state electronics.

The LARC architecture supported multiprocessing with two CPUs (called Computers) and an input/output (I/O) Processor (called the Processor). Two LARC machines were built, the first delivered to Livermore in June 1960, and the second to the Navy's David Taylor Model Basin. Both examples had only one CPU, so no multiprocessor LARCs were ever built.[2] Livermore decommissioned their LARC in December 1968[3] and the Navy's LARC was turned off in April 1969.[4]

The LARC CPUs were able to perform addition in about 4 microseconds, corresponding to about 250 kIPS speed. This made it the fastest computer in the world until 1962 when the IBM 7030 Stretch took the title. The 7030 started as IBM's entry to the LARC contest, but Teller chose the simpler Univac over the riskier IBM design.

Description

The LARC was a decimal mainframe computer with 60 bits per word. It used bi-quinary coded decimal arithmetic with five bits per digit (see below), allowing for 11-digit signed numbers. Instructions were 60 bits long, one per word. The basic configuration had 26 general-purpose registers, which could be expanded to 99. The general-purpose registers had an access time of one microsecond.

LARC weighed about 115,000 pounds (58 short tons; 52 t).[5]

The basic configuration had one Computer and LARC could be expanded to a multiprocessor with a second Computer.

The Processor is an independent CPU (with a different instruction set from the Computers) and provides control for 12 to 24 magnetic drum storage units, four to forty UNISERVO II tape drives, two electronic page recorders (a 35mm film camera facing a cathode-ray tube), one or two high-speed printers, and a high-speed punched card reader.

The LARC used core memory banks of 2500 words each, housed four banks per memory cabinet. The basic configuration had eight banks of core (two cabinets), 20,000 words. The memory could be expanded to a maximum of 39 banks of core (ten cabinets with one empty bank), 97,500 words. The core memory had one parity bit on each digit for error checking, resulting in 60 bits per memory word. The core memory had an access time of 8 microseconds and a cycle time of 4 microseconds. Each bank operated independently and could begin a new access in any 4-microsecond cycle when it was not already busy. By properly interleaving accesses to different banks the memory could sustain an effective access time of 4 microseconds on each access (e.g., instruction access in one bank data in another).

The data transfer bus connecting the two Computers and the Processor to the core memory was multiplexed to maximize throughput; every 4-microsecond bus cycle was divided into eight 500-nanosecond time slots:

- Processor - instructions and data

- Computer 1 - instructions

- Computer 2 - data

- I/O DMA Synchronizer - data

- Not Used

- Computer 2 - instructions

- Computer 1 - data

- I/O DMA Synchronizer - data

The core memory system enforces a system of interlocks and priorities to avoid simultaneous access of the same memory bank by multiple sections of the system (the Computers, Processor, and I/O DMA Synchronizers) without conflicts or deadlocks. A memory bank is unavailable for one 4-microsecond cycle after being addressed by any section of the system. If another section attempts to address the same memory bank during this time, it is locked out and must wait, then try again in the next 4-microsecond cycle. To prevent deadlocks and timeouts in the I/O system the following priorities are enforced:

- I/O DMA Synchronizer - highest

- Processor

- Computers - lowest

If a higher-priority section is locked out in one 4-microsecond cycle, when it tries again in the next 4-microsecond cycle, all lower-priority sections are prevented from beginning a new cycle on that memory bank until the higher-priority section has completed its access.

The LARC's Computers wrote lists of Summary Orders in memory for the Processor to read and interpret by the Processor Control Program (written and supplied by UNIVAC with each system), to request needed I/O.[6]

The LARC was built using surface-barrier transistors, which were already obsolete by the time the first system was delivered. The LARC was a very fast computer for its time. Its addition time was 4 microseconds, multiplication time was 8 microseconds, and the division time was 28 microseconds. It was the fastest computer in 1960–61, until the IBM 7030 took the title.

LARC one-digit numeric code

In the basic five-bit biquinary code of the UNIVAC-LARC, 15 combinations are allowed, any one of which may be stored in any digit position in storage.[7]

| BIT POSITIONS

|

CHARACTER |

|---|---|

1 1 1 0 0

|

\ (ignore) |

0 0 1 0 0

|

^ (space) |

0 0 0 1 0

|

- (minus) |

1 0 0 0 0

|

0 |

0 0 0 0 1

|

1 |

1 0 0 1 1

|

2 |

0 0 1 1 1

|

3 |

1 0 1 1 0

|

4 |

0 1 0 0 0

|

5 |

1 1 0 0 1

|

6 |

0 1 0 1 1

|

7 |

1 1 1 1 1

|

8 |

0 1 1 1 0

|

9 |

1 1 0 1 0

|

. (period) |

1 0 1 0 1

|

+ (plus) |

See also

References

- ↑ The Remington Rand Univac LARC

- ↑ George Gray (March 1999). "Some Burroughs Transistor Computers". Unisys History Newsletter 3 (1). https://wiki.cc.gatech.edu/folklore/index.php/Some_Burroughs_Transistor_Computers.

- ↑ "Were Early Giant Computers a Success?". Datamation: 77–82. April 1969. http://www.bitsavers.org/magazines/Datamation/196904.pdf. "After their installation, the two systems remained in continuous use until December 1968, when the Lawrence Radiation Laboratory retired its LARC system which had been operated on a 7-day-per-week, 24-hour-per-day schedule.".

- ↑ Smith, Ruth C. (1974). "Special Libraries, February 1974". Special Libraries 65 (2): 61–65. https://scholarworks.sjsu.edu/sla_sl_1974/2/. Retrieved 5 June 2024.

- ↑ Weik, Martin H. (Mar 1961). "UNIVAC LARC". http://www.ed-thelen.org/comp-hist/BRL61-u3.html#UNIVAC-LARC.

- ↑ (in English) Summary Orders for a Processor Program, UNIVAC LARC Programming. UNIVAC. pp. 1–5.

- ↑ (in English) General Description The UNIVAC®-LARC System. UNIVAC. pp. 6–7.

Further reading

- From Dits to Bits: A personal history of the electronic computer. Portland, Oregon, USA: Robotics Press. 1979. ISBN 0-89661-002-0. https://archive.org/details/fromditstobitspe0000luko.

- Lundstrom, David E. (1987). A few good men from Univac. Cambridge, Mass. : MIT Press. ISBN 978-0-262-12120-0. https://archive.org/details/fewgoodmenfromun00lund/. Retrieved 12 May 2024.

- Fisher, Franklin M.; MacKie, James W.; Mancke, Richard B. (1983). IBM and the U.S data processing industry: an economic history. New York, N.Y., U.S.A: Praeger. pp. 57–59. ISBN 9780030630590. https://archive.org/details/ibmusdataprocess0000fish. Retrieved 16 September 2023.

External links

- Margaret R. Fox Papers, 1935–1976, Charles Babbage Institute, University of Minnesota. collection contains reports, including the original report on the ENIAC, UNIVAC, and many early in-house National Bureau of Standards (NBS) activity reports; memoranda on and histories of SEAC, SWAC, and DYSEAC; programming instructions for the UNIVAC, LARC, and MIDAC; patent evaluations and disclosures relevant to computers; system descriptions; speeches and articles written by Margaret Fox's colleagues.

- Universal Automatic Computer Model LARC

- LARC Manuals and documentation

| Records | ||

|---|---|---|

| Preceded by IBM 7090 |

World's most powerful computer 1960–1961 |

Succeeded by IBM 7030 Stretch |

|