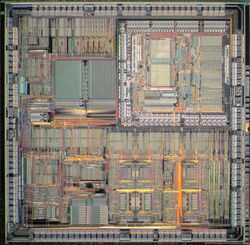

Engineering:Freescale 683XX

The Freescale 683xx (formerly Motorola 683xx) is a family of compatible microcontrollers by Freescale that use a Motorola 68000-based CPU core. The family was designed using a hardware description language, making the parts synthesizable, and amenable to improved fabrication processes, such as die shrinks.

There are two CPU cores used in the 683xx family: the 68EC000 and the CPU32. The instruction set of the CPU32 core is similar to the 68020 without bitfield instructions, and with a few instructions unique to the CPU32 core, such as table lookup and interpolate instructions, and a low-power stop mode.

The modules of the microcontroller were designed independently and released as new CPUs could be tested. This process let the architects perform "design-ahead" so that when silicon technologies were available, Motorola had designs ready to implement and go to market. Many of these submodules have been carried forward into the Coldfire line of processors.

The microcontrollers consist of a series of modules, connected by an internal bus:

- A fully static CPU core, capable of running at any clock speed from dead stop to maximum rated speed (25 or 33MHz).

- A CPU core designed to minimize transistors while maximizing performance.

- A high-speed clocked serial interface for debugging called background debug mode (BDM). The 683xx-series was the first to have a clocked serial interface to the CPU to perform debugging. Now, many CPUs use a standard serial test interface, usually JTAG, for this purpose.

- The SIM (System Integration Module), which eliminates much glue logic by providing chip selects and address decoding. The SIM also provides a clock generator, watchdogs for various system operations, configuration of processor pins, a periodic timer, and an interrupt controller.

Other modules available on various processors in the 683xx family are:

- The Timing Processor Unit (TPU), which performs almost any timing related task: timers, counters, proportional pulse width control, pulse width measurement, pulse generation, stepper motor controllers, quadrature detection, etc. Freescale gives the development system and code away for free.

- An auxiliary random-access memory (RAM) doubles as a programmable microcontroller store for the TPU.

- Some early models have two conventional counter-timers.

- A general purpose timer (GPT) module provides pulse accumulators, capture/compare, and pulse-width modulation capabilities.

- Some models have a network interface processor in the form of a communication processor module (CPM) and serial communications controllers (SCC) which can be interfaced to Ethernet or HDLC busses.

- Most models have a queued serial module (QSM) which provides both synchronous Serial Peripheral Interface (SPI), and logic-level RS232 UART capabilities.

See also

- QUICC (Quad Integrated Communications Controller)

External links