Engineering:Motorola 68040

| General Info | |

|---|---|

| Launched | 1990 |

| Designed by | Motorola |

| Performance | |

| Max. CPU clock rate | 25 MHz to 40 MHz |

| Data width | 32 bits |

| Address width | 32 bits |

| Cache | |

| L1 cache | 4096 bytes each for instruction and data with independent MMU and TLB[1] |

| Architecture and classification | |

| Instruction set | Motorola 68000 series |

| Physical specifications | |

| Transistors |

|

| Package(s) | |

| Products, models, variants | |

| Variant(s) | 68LC040 and 68EC040 |

| History | |

| Predecessor | Motorola 68030 |

| Successor | Motorola 68060 |

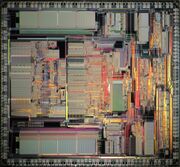

The Motorola 68040 ("sixty-eight-oh-forty") is a 32-bit microprocessor in the Motorola 68000 series, previewed in April 1989,[2] announced in January 1990,[3] but only available from late 1990 in limited volumes.[4] It is the successor to the 68030 and is followed by the 68060, skipping the 68050. In keeping with general Motorola naming, the 68040 is often referred to as simply the '040 (pronounced oh-four-oh or oh-forty).

The 68040 was the first 680x0 family member with an on-chip Floating-Point Unit (FPU). It thus included all of the functionality that previously required external chips, namely the FPU and Memory Management Unit (MMU), which was added in the 68030. It also had split instruction and data caches of 4 kilobytes each. It was fully pipelined, with six stages.[5]

Versions of the 68040 were created for specific market segments, including the 68LC040, which removed the FPU, and the 68EC040, which removed both the FPU and MMU. Motorola had intended the EC variant for embedded use, but embedded processors during the 68040's time did not need the power of the 68040, so EC variants of the 68020 and 68030 continued to be common in designs.

Motorola produced several speed grades. The 16 MHz and 20 MHz parts were never qualified (XC designation) and used as prototyping samples. 25 MHz and 33 MHz grades featured across the whole line, but until around 2000 the 40 MHz grade was only for the "full" 68040. A planned 50 MHz grade was canceled after it exceeded the thermal design envelope.

A per-unit price of US$795 (equivalent to about $1,900 in 2024) was reported at launch announcement in early 1990.[3] This fell to $595 for volume production in late 1990.[4] By late 1992, pricing of the 25 MHz part had fallen to $337,[6] comparable to the $328 price of Intel's 33 MHz 80486DX.[7]

Usage

In Apple Macintosh computers, the 68040 was introduced in the Macintosh Quadra, which was named for the chip. The fastest 68040 processor was clocked at 40 MHz and it was used only in the Quadra 840AV. The more expensive models in the (short-lived) Macintosh Centris line also used the 68040, while the cheaper Quadra, Centris, Performa, and some late-model LC used the 68LC040.

The 68040 was also used in other personal computers, such as the Amiga 4000 and Amiga 4000T, as well as a number of workstations, Alpha Microsystems servers, the HP 9000/400 series, NCR Corporation's TOWER 32/750, 32/825 and 32/850,[8] Apollo Computer's DN5500,[9] and later versions of the NeXT computer.

The 68040 processor is used in the flight management computers (FMC) aboard many Boeing 737 aircraft, including all Next Generation and MAX models,[10] and in the flight control system of Saab JAS 39 Gripen.[11]

Design

The 68040 ran into the transistor budget limit early in design. While the MMU did not take many transistors—indeed, having it on the same die as the CPU actually saved on transistors—the FPU certainly did. Motorola's 68882 external FPU was known as a very high performance unit and Motorola did not wish to risk integrators using the "LC" version with a 68882 instead of the more profitable full "RC" unit. (For information on Motorola's multiprocessing model with the 680x0 series, see Motorola 68020.) The FPU in the 68040 was incapable of IEEE transcendental functions, which had been supported by both the 68881 and 68882 and were used by the popular fractal generating software of the time and little else. The Motorola floating-point support package (FPSP) emulated these instructions in software under interrupt. As this was an exception handler, heavy use of the transcendental functions caused severe performance penalties.

Heat was always a problem throughout the 68040's life. While it delivered over four times the per-clock performance of the 68020 and 68030, the chip's complexity and power requirements came from a large die and large caches. This affected the scaling of the processor and it was never able to run with a clock rate exceeding 40 MHz. A 50 MHz variant was planned, but canceled. Overclocking enthusiasts reported success reaching 50 MHz using a 100 MHz oscillator instead of an 80 MHz part and the then novel technique of adding oversized heat sinks with fans.

The 68040 offered the same features as the 80486, but on a clock-for-clock basis could significantly outperform the Intel chip in integer and floating-point instructions according to Motorola's own benchmark results.[3][12][13][14] Independent measurements of the processor's floating-point performance in workstation systems suggested rather more modest gains over the 80486 and SPARC in Motorola's chosen LINPACK benchmark, largely confined to double-precision operations,[15] and vendor literature such as that describing the NeXTstation Color and Turbo Color models advertised somewhat lower ratings than Motorola's own literature.[16][note 1]

However, the 80486 had the ability to be clocked significantly faster without suffering from overheating problems, and also quickly spawned a mobile derivative for laptops. Newer-generation 80486-based PC laptops were introduced in 1992, resulting in the 100-series PowerBook being stuck with the aging 68030 which were no longer competitive, and Apple was unable to ship a 68040-equipped PowerBook until the PowerBook Duo 280 and PowerBook 500 series in 1994. [17][18]

Variants

68EC040

The 68EC040 is a version of the Motorola 68040 microprocessor, intended for embedded controllers (EC). It differs from the 68040 in that it has neither an FPU nor an MMU. This makes it less expensive and it draws less power. The 68EC040 was used in Cisco switch Supervisor Engine I that is the heart of models 2900, 2948G, 2980G, 4000, 4500, 5000, 5500, 6000, 6500 and 7600.

68LC040

The 68LC040 is a low cost version of the Motorola 68040 microprocessor with no FPU. This makes it less expensive and it draws less power. Although the CPU now fits into a feature chart more like the Motorola 68030, it continues to include the 68040's caches and pipeline and is thus significantly faster than the 68030.

Some mask revisions of the 68LC040 contained a bug that prevents the chip from operating correctly when a software FPU emulator is used. According to Motorola's errata,[19] any chip with a mask set 2E71M or later does not contain the bug. This new mask was introduced in mid-1995 and converted the 68LC040 chip to MC status.[20]

The buggy revisions are typically found in 68LC040-based Apple Macintosh computers. Chips with mask set 2E23G (as used in the LC 475) have been confirmed to be faulty. The fault relates to pending writes being lost when the F-line exception is triggered.[21] The 68040 cannot update its microcode in the manner of modern x86 chips. This means that the only way to use software that requires floating-point functionality is to replace the buggy 68LC040 with a later revision, or a full 68040.

Feature table

| Variant | MMU | FPU |

|---|---|---|

| 68040 | Yes | Yes |

| 68LC040 | Yes | No |

| 68EC040 | No | No |

Technical data

| CPU clock rate | 25, 33, 40 MHz |

| Production process | static CMOS 0.8 μm, 0.65 μm, Freescale 0.57 μm |

| Chip carrier | 179 ceramic PGA and 184 QFP |

| Address bus | 32 bit |

| Data bus | 32 bit |

| Instruction set | CISC |

| Transistors | ~1,200,000 |

See also

- List of Mac models grouped by CPU type

References

- ↑ "MC68040 Product Summary Page". http://www.freescale.com/webapp/sps/site/prod_summary.jsp?code=MC68040.

- ↑ "...as Motorola Steals Intel Thunder with 68040 Preview". Unigram/X: pp. 1. 1 April 1989. https://archive.org/details/UnigramX1989212-262/page/n74/mode/1up.

- ↑ 3.0 3.1 3.2 Daly, James (22 January 1990). "Motorola introduces 68040 high-end chip". Computerworld: 133. https://archive.org/details/sim_computerworld_1990-01-22_24_4/page/133/mode/1up. Retrieved 3 March 2024.

- ↑ 4.0 4.1 "Enfin le Motorola 68040...". Unigram/X: pp. 1. 3 December 1990. https://archive.org/details/UnigramX1990263-313/page/n316/mode/1up.

- ↑ This article is based on material taken from Motorola+68040 at the Free On-line Dictionary of Computing prior to 1 November 2008 and incorporated under the "relicensing" terms of the GFDL, version 1.3 or later.

- ↑ "Motorola 680x0". EDN: 140. November 1992. https://archive.org/details/edn-1992_11_26/page/n139/mode/1up. Retrieved 12 February 2026.

- ↑ "Intel 80386/80486". EDN: 140. November 1992. https://archive.org/details/edn-1992_11_26/page/n131/mode/1up. Retrieved 12 February 2026.

- ↑ Fitzgerald, Michael (May 6, 1991). "NCR promises Tower line lives". Computerworld. https://archive.org/details/sim_computerworld_1991-05-06_25_18/page/n115. Retrieved 31 Mar 2023.

- ↑ Tim Hunkler (July 1996). "Survival Guide for Apollo Workstations". https://web-docs.gsi.de/~kraemer/COLLECTION/www.hunkler.com/aegis/aegis_sg.html.

- ↑ Brady, Chris. "The Boeing 737 Flight Management Computer". http://www.b737.org.uk/fmc.htm.

- ↑ Frisberg, Bo, Usage of Ada in the Gripen Flight Control System, pp. 1, https://www.sigada.org/conf/sa98/papers/frisberg.pdf, retrieved 9 December 2025

- ↑ Tabak, Daniel (1991). Advanced Microprocessors. McGraw-Hill Inc.. pp. 506–507. ISBN 0-07-062807-6. https://archive.org/details/advancedmicropro00dani/page/506/mode/2up. Retrieved 30 January 2026.

- ↑ "CISC: The Intel 80486 vs. The Motorola MC68040". July 1992. http://textfiles.meulie.net/computers/486vs040.txt.

- ↑ "68040 Microprocessor". http://www.bbs.ingedigit.com.ve/TechInfo/68040.Microprocessor.html.

- ↑ Wilson, David (May 1991). "Tested Mettle: Hewlett-Packard 9000/425t". UNIX Review: 63–67. https://archive.org/details/sim_unix-review_1991-05_9_5/page/63/mode/1up. Retrieved 30 January 2023.

- ↑ NeXTstation Color/NeXTstation Turbo Color. NeXT Computer Inc.. 1992. pp. 4. https://archive.org/details/NeXTSpecSheets/NeXTstationColor/page/n3/mode/2up. Retrieved 30 January 2026.

- ↑ "Kunkel, Paul, AppleDesign: The work of the Apple Industrial Design Group, with photographs by Rick English, New York: Graphis, 1997, p.30

- ↑ "Birth of the Powerbook". Low End Mac. July 12, 2016. http://lowendmac.com/2016/birth-of-the-powerbook-how-apple-took-over-the-portable-market-in-1991/.

- ↑ "Documentation Clarification for MC68040". http://www.freescale.com/files/microcontrollers/doc/errata/MC68040DE_D.txt.

- ↑ "E71M and E42K MC-Qualified Mask Sets". http://www.freescale.com/files/shared/doc/pcn/PCNR00274.html.

- ↑ "NetBSD Problem Report #13078: Mac 68LC040 problem". Gnats.netbsd.org. http://gnats.netbsd.org/13078.

Notes

- ↑ NeXT literature gives a LINPACK (dp) rating of 2.2 MFLOPS for the 25 MHz model and 2.9 MFLOPS for the 33 MHz model, in contrast to Motorola's claim of 3.0 MFLOPS featured in Advanced Microprocessors.

Further reading

- "The Decimal Floating-Point Standard". quadibloc. 2018. Other Recent Decimal Floating-Point Formats. http://www.quadibloc.com/comp/cp020302.htm.

External links

- MC68040V Third-Generation 32-Bit Low-Power Microprocessor (PDF)

- M68040 Microprocessors User's Manual (PDF)

|