Engineering:ANTIC

Alphanumeric Television Interface Controller[1] (ANTIC) is an LSI ASIC dedicated to generating 2D computer graphics to be shown on a television screen or computer display. Under the direction of Jay Miner, the chip was designed in 1977–1978 by Joe Decuir, Francois Michel, and Steve Smith[2] for the Atari 8-bit family of home computers first released in 1979 and was patented by Atari, Inc. in 1981.[3] ANTIC is also used in the 1982 Atari 5200 video game console, which shares most of the same hardware as the 8-bit computers.

For every frame of video, ANTIC reads a program of instructions to define the playfield, or background graphics, then delivers a data stream to the companion CTIA or GTIA chip which adds color and overlays sprites (referred to as "Player/Missile graphics" by Atari). Each ANTIC instruction corresponds to either blank scan lines or one of 14 graphics modes used for a horizontal band of the display. The height of each band depends on the mode. A full program, or display list in Atari parlance, specifies the entire display built from a stack of individual modes.

The display list also specifies where the data for each row comes from. For character modes, the base address of the character bitmaps themselves is stored in an on-chip register and can be changed. Display list instructions can also enable horizontal and vertical fine scrolling and mark that an interrupt should occur. An interrupt allows arbitrary 6502 code to execute, usually to change display-related settings in the middle of a frame.

Atari computer magazine Antic was named after the chip.[4]

Features

The list below describes ANTIC's inherent hardware capabilities meaning the intended functionality of the hardware by itself, not including results achieved by CPU-serviced interrupts or display kernels frequently driving register changes.

ANTIC uses DMA to read a program called the display list which specifies these playfield features:

- 14 different graphics modes

- 6 character modes

- 4 types of font/glyph rendering

- 8 bitmapped modes

- 6 character modes

- Output a variable number of blank scan lines

- Playfield Text and Map modes can be mixed onscreen

- Variable screen height up to vertical overscan

- Horizontal and Vertical coarse scrolling

- Identify sections of the display subject to Horizontal and/or Vertical Fine scrolling

- Trigger a CPU-serviced interrupt routine, called the "Display List Interrupt", at specific scan lines (also called "raster interrupt" or "Horizontal Blank Interrupt" on other systems)

- Trigger a CPU-serviced interrupt routine, called the "Vertical Blank Interrupt", at the end of the display frame.

Other register-based functions:

- Variable screen width up to horizontal overscan

- Define the distance of movement for Horizontal and Vertical Fine scrolling

- Provides real-time information of the electron beam's vertical screen location.

- Reads a light pen horizontal/vertical coordinates (CRT only)

- Soft, re-definable character set.

- Adjustable display of inverse video characters.

- Characters may be vertically reflected.

- Control the display-oriented Vertical Blank and Display List interrupts, and the Reset key interrupt.

- Performs DMA for CTIA/GTIA to produce Player/Missile graphics (aka sprites)

- Non-fixed RAM. This allows RAM for graphics features to be located almost anywhere in the 16-bit memory address range. This applies to:

- Display lists.

- Playfield graphics data

- Character set fonts

- Player/Missile graphics data

Versions

by part number

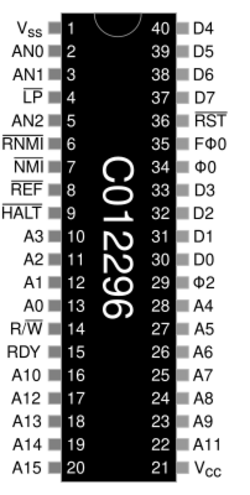

- C012296 — NTSC: Used in Atari 400, 800, and 1200XL computers.[5]

- C014887 — PAL/SECAM: Used in Atari 400 and 800 computers.

- C021697 — NTSC: Used in Atari 600XL, 800XL, and XE models.

- C021698 — PAL/SECAM: Used in Atari XL, and XE models.

Atari, Inc. intended to combine functions of the ANTIC and GTIA chips in one integrated circuit to reduce production costs of Atari computers and 5200 consoles. Two such prototype circuits were being developed, but neither entered production.

Pinout

| Pin name | Pin number(s) | Description |

|---|---|---|

| A0 - A15 | 13, 12, 11, 10, 28, 27, 26, 25, 24, 23, 16, 22, 17, 18, 19, 20 | Memory address I/O |

| AN0 – AN2 | 2, 3, 5 | ANTIC interface to CTIA/GTIA |

| D0 – D7 | 30, 31, 32, 33, 40, 39, 38, 37 | Data bus I/O |

| FØ0 | 35 | Fast phase 0 input clock |

| HALT | 9 | Halt output (suspends CPU while ANTIC reads memory) |

| LP | 4 | Light pen input |

| NMI | 7 | NMI interrupt output to CPU |

| RDY | 15 | Ready output. ANTIC pulls pin low to halt the CPU for horizontal blank syncing (WSYNC) |

| REF | 8 | RAM refresh output |

| RNMI | 6 | NMI interrupt input |

| RST | 36 | Reset ANTIC input |

| R/W | 14 | Read/write I/O direction |

| Vcc | 21 | Power +5 volts |

| Vss | 1 | Ground |

| Ø0 | 34 | Phase 0 clock output |

| Ø2 | 29 | Phase 2 input clock |

Registers

The Atari 8-bit computers and the Atari 5200 console map the ANTIC chip to the $D4xxhex page.

ANTIC provides 15 Read/Write registers controlling Playfield display parameters, DMA for Player/Missile graphics, fine scrolling, light pen input, and interrupts. Hardware registers do not return the written values back when read. This problem is solved by Operating System Shadow registers implemented in regular RAM as places to store the last value written to registers. Operating System Shadow registers are copied from RAM to the hardware registers during the vertical blank. Therefore, any writes to hardware registers which have corresponding shadow registers will be overwritten by the value of the Shadow registers during the next vertical blank.

Some Write hardware registers do not have corresponding Shadow registers. They can be safely written by an application without the value being overwritten during the vertical blank. If the application needs to know the last state of the register then it is the responsibility of the application to remember what it wrote.

Operating System Shadow registers also exist for some Read registers where reading the value directly from hardware at an unknown stage in the display cycle may return inconsistent results.

| Name | Description | Read/Write | Hex Addr | Dec Addr | Shadow Name | Shadow Hex Addr | Shadow Dec Addr |

|---|---|---|---|---|---|---|---|

| DMACTL | Direct Memory Access Control | Write | $D400 | 54272 | SDMCTL | $022F | 559 |

| CHACTL | Character Control | Write | $D401 | 54273 | CHART | $02F3 | 755 |

| DLISTL | Display List Pointer (low byte) | Write | $D402 | 54274 | SDLSTL | $0230 | 560 |

| DLISTH | Display List Pointer (high byte) | Write | $D403 | 54275 | SDLSTH | $0231 | 561 |

| HSCROL | Horizontal Fine Scroll | Write | $D404 | 54276 | |||

| VSCROL | Vertical Fine Scroll | Write | $D405 | 54277 | |||

| PMBASE | Player/Missile Base Address | Write | $D407 | 54279 | |||

| CHBASE | Character Set Base Address | Write | $D409 | 54281 | CHBAS | $02F4 | 756 |

| WSYNC | Wait for Horizontal Sync | Write | $D40A | 54282 | |||

| VCOUNT | Vertical Line Counter | Read | $D40B | 54283 | |||

| PENH | Light Pen Horizontal Position | Read | $D40C | 54284 | LPENH | $0234 | 564 |

| PENV | Light Pen Vertical Position | Read | $D40D | 54285 | LPENV | $0235 | 565 |

| NMIEN | Non-Maskable Interrupt (NMI) Enable | Write | $D40E | 54286 | |||

| NMIRES | Non-Maskable Interrupt (NMI) Reset | Write | $D40F | 54287 | |||

| NMIST | Non-Maskable Interrupt (NMI) Status | Read | $D40F | 54287 |

In the individual register listings below the following legend applies:

| Bit Value | Description |

|---|---|

| 0 | Bit must be 0 |

| 1 | Bit must be 1 |

| ? | Bit may be either 0 or 1, and is used for a purpose. |

| - | Bit is unused, or should not be expected to be a certain value |

| label | Refer to a later explanation for the purpose of the bit. |

DMACTL $D400 Write

SHADOW: SDMCTL $022F

Direct Memory Access (DMA) Control

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---|---|---|---|---|---|---|---|

| - | - | Display List DMA | Player Missile Resolution | Player DMA | Missile DMA | Playfield Width | Playfield Width |

DMACTL controls ANTIC's DMA behavior for the Playfield and Player-Missile (sprite) graphics.

Playfield Width bit values:

| Playfield Width Bits [1:0] | Description | Size |

|---|---|---|

| 0 0 = $00 | Disable playfield | |

| 0 1 = $01 | Narrow playfield | 128 color clocks/256 high-res pixels |

| 1 0 = $02 | Normal playfield | 160 color clocks/320 high-res pixels |

| 1 1 = $03 | Wide playfield | 192 color clocks/384 high-res pixels |

Also see Display List DMA bit regarding Playfield display.

Player/Missile DMA bits values:

| Player/Missile DMA Bits [3:2] | Description |

|---|---|

| 0 0 = $00 | Disable Player and Missile DMA |

| 0 1 = $04 | Enable Missile DMA |

| 1 0 = $08 | Enable Player DMA |

| 1 1 = $0C | Enable Player and Missile DMA |

ANTIC's Player/Missile DMA feature reads bytes from memory and delivering data to update CTIA/GTIA's GRAFP0, GRAFP1, GRAFP2, GRAFP3, and GRAFM graphics pattern registers relieving the CPU from creating Player/Missile (sprite) graphics. These bits turn on ANTIC's transmission of Player data and Missile data to CTIA/GTIA. CTIA/GTIA must also be configured to receive the data via its GRACTL register in order for Player/Missile DMA to function as expected.

When Player DMA is enabled, Missile DMA automatically occurs to keep the DMA timing consistent, but the data is not delivered to the Missile's GRAFM register.

When enabled, Player/Missile DMA occurs on every scan line in the visible display—from scan line 8 to 247. Therefore, the Player/Missile data in the memory map (see ANTIC's PMBASE) above and below those scan line counts is unused and undisplayed.

Player/Missile Resolution bit values:

- $00 - Double line resolution. ANTIC updates its DMA fetch address every other scan line and updates the CTIA/GTIA Player/Missile Graphics pattern registers every scan line, so that each Player/Missile byte pattern is two scan lines tall. When Double line resolution is enabled CTIA/GTIA register VDELAY ($D01Chex/53276dec) works by masking updates on even scan lines which results in shifting the bit pattern of individual Players and Missiles down one scan line.

- $10 - Single line resolution. A DMA fetch and Player/Missile register update occurs on every scan line. CTIA/GTIA register VDELAY ($D01Chex/53276dec) which masks updates on even scan lines effectively reduces Single line resolution to Double line resolution.

ANTIC DMA and Player/Missile pattern register updates occur on each scan line regardless of resolution. When Double line resolution is in effect the Player/Missile memory can be modified between the redundant DMA fetches thus changing the pattern sent to the GRAF* registers and producing apparent Single line resolution Player/Missiles.

Display List DMA bit values:

- $00 - Disable Display List.

- $20 - Enable Display list.

Playfield display requires that Display List DMA is enabled, and a Playfield width specified. If either value is zero, then no Playfield display is generated.

CHACTL $D401 Write

SHADOW: CHART $02F3

Character Control

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---|---|---|---|---|---|---|---|

| - | - | - | - | - | Video Reflect | Video Inverse | Video Blank |

CHACTL controls character display.

Character control bit values do the following actions:

| Feature | Bits Value | Description |

|---|---|---|

| Video Blank | $01 | Inverse video characters display as blanks spaces. |

| Video Inverse | $02 | Inverse video characters appear as inverse video. (default) |

| Video Reflect | $04 | All characters are displayed vertically mirrored. |

The CHACTL Video Inverse and Video Blank bits affect the display of characters in ANTIC Text Modes 2 and 3 which have the high bit set (characters $80 through $FF). Toggling the values of the CHACTL bits allow blinking or blanking these characters globally for the entire display.

Video Inverse and Video Blank enabled together result in reverse video characters displayed as an inverse blank space. Video Inverse and Video Blank bits work in ANTIC modes 2 and 3, and have no effect on the other text modes 4, 5, 6, and 7.

The Video Reflect bit affects all Text Modes. Video Reflect is useful for situations requiring mirroring effects without defining a new character set. An ideal use is card games displaying accurate card faces showing upside down suits. As this vertically mirrors the glyph data before it is used, the effect appears inconsistent for ANTIC Mode 3 descenders with glyph bytes 6 and 7 appearing at the bottom of the descender area.

DLISTL/DLISTH $D402/$D403 Write

SHADOW: SDLSTL/SDLSTH $0230/$0231

Display List Pointer

| Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ? | ? | ? | ? | ? | ? | ? | ? | ? | ? | ? | ? | ? | ? | ? | ? |

ANTIC begins executing the Display List pointed to by the 16-bit address in registers DLISTL/DLISTH (D402-D403hex/54274-54275dec). The address registers are updated during Display List execution by ANTIC's JMP (Jump) and JVB (Jump and wait for Vertical Blank). The address is also updated by the Operating System's Vertical Blank Interrupt (VBI) routine using the values in shadow registers SDLSTL/SDLSTH (0230-0231hex/560-561dec).

When the OS Vertical Blank Interrupt is enabled, direct updates to the ANTIC DLIST registers by the CPU or the ANTIC Jump instructions will be overwritten by the OS during the next Vertical Blank by the values in the shadow registers. Therefore, page flipping implemented by Display Lists that point to the next Display List in series will not operate as expected unless the Vertical Blank interrupt is disabled.

HSCROL $D404 Write

Horizontal Fine Scroll

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---|---|---|---|---|---|---|---|

| — | — | — | — | ? | ? | ? | ? |

This register specifies the distance of the Horizontal fine scrolling shift in color clocks. Only the lowest 4 bits are significant. The value range of 16 color clocks allows ANTIC to shift Mode 2 Text four characters, and Mode 6 text two characters before a coarse scroll is needed.

When Horizontal scrolling is enabled for a mode line ANTIC fetches the next size increment greater than the current screen width to provide the buffer of data subject to the horizontal scrolling control. When displaying Narrow width ANTIC fetches the screen RAM needed for Normal width. Likewise, for Normal width ANTIC fetches the screen RAM needed for Wide.

ANTIC buffers the first few bytes read from screen memory that are sufficient to cover the 16 color clock range of movement. (Two to four bytes depending on display mode.) The HSCROL value specifies how many color clocks should be output from the buffered data beginning from the last (right most) color clock of the last buffered byte and progressing to the left. When HSCROL is 0 no color clocks are output from the buffer, so the first screen byte displayed is the first byte after the buffered data. As HSCROL increases more color clocks from the end (right side) of the buffered data are added to the left edge of the display causing the fine scroll shift to move the screen contents to the right.

ANTIC Mode F (high-resolution, 1/2 color clock pixels) can only be scrolled two pixels at a time, because HSCROL specifies color clocks.

ANTIC Modes using the alternate GTIA color interpretations must be scrolled by an entire GTIA pixel (two color clocks). Only even values should be used to ensure correct scrolling. Odd values of HSCROL will shift the pixel stream into a different state that GTIA will interpret as different colors.

Unlike many platforms Atari's horizontal scrolling is visually consistent and free from color "strobing" artifacts due to Atari's pixel size matching the color clock timing needed for accurate color.

VSCROL $D405 Write

Vertical Fine Scroll

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---|---|---|---|---|---|---|---|

| — | — | — | — | ? | ? | ? | ? |

This register specifies the distance of the Vertical fine scrolling in scan lines. The lowest 4 bits are significant, however the Vertical scroll value should range from 0 to the ANTIC Mode line's scan line height - 1. Scrolling farther than the ANTIC Mode's number of scan lines results in lines of repeated data upsetting the fine scrolling continuity (though, this can also be used as an exploitable behavior).

The Vertical scrolling region is defined by setting the VS bit ($20) on a sequential series of ANTIC Mode Lines in the Display List. The first Mode line without the VS bit set becomes the end of the scrolling region and is used as a buffer line to supply the new information to scroll up into the bottom of the scrolling region.

The Vertical scroll value indicates the scan line number to begin the display in the first Mode line and is also used as the scan line number to end the display in the last Mode line (the line without the VS bit set).

Example: Given an eight scan line ANTIC Mode (Text Modes 2, 4, or 6) with the VS bit set on two adjacent Mode lines the scrolling region then consists of three Mode lines—the third line in the scrolling region is the first Mode line encountered without the VS bit set. When Vertical scrolling is not set in the Display List the three Modes lines would naturally result in 24 displayed scan lines. When the VS bits are set in the Display List Mode instructions as described and the VSCROL value is set to 2 then the first Mode line in the region begins displaying at scan line 2 showing scan lines 2 to 7 (six scan lines or 8 - VSCROL), the second Mode line is displayed completely (eight scan lines), and the final Mode line ends at scan line 2 showing scan lines 0 to 2 (three scan lines or VSCROL + 1). The total scan lines displayed in the scrolling region is then 6 + 8 + 3 = 17 scan lines.

Since fine scrolling is based on scan lines not pixel height, and scrolling region movement is done simply by skipping scan lines from the first Mode line and adding scan lines to the last Mode line, it is possible to use different graphics Modes within the scrolling region. This merely requires additional care when determining how many scan lines can be shifted for the current first and last Mode lines in the scrolling region.

Blank Mode lines cannot be contained within a scrolling region, because Blank Mode line instructions inherently do not have a Vertical Scroll Modifier bit. (Blank Mode line instructions specify the blank line count using the bits 7 through 5 that function as LMS, HS, and VS Modifiers for "regular" Playfield Mode instructions.) However, a Blank Mode instruction can be used to end a scrolling region and is still subject to the expected scan line height changes per the vertical scroll value.

PMBASE $D407 Write

Player Missile Base Address

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---|---|---|---|---|---|---|---|

| ? | ? | ? | ? | ? | ? | ? | ? |

This specifies the page of the base address for Player/Missile graphics. When double line resolution P/M graphics are operating the PMBASE value must begin on a 1K boundary. When single line resolution P/M graphics are operating the PMBASE value must begin on a 2K boundary.

CHBASE $D409 Write

SHADOW: CHBAS $02F4

Character Base Address

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---|---|---|---|---|---|---|---|

| ? | ? | ? | ? | ? | ? | ? | ? |

This specifies the page of the base address for the character set. ANTIC Modes 2, 3, 4, and 5 use 128 characters in the character set and require the CHBASE value begin on a 1K boundary. ANTIC Modes 6 and 7 use 64 characters, so the CHBASE value must begin on a 512 byte boundary.

The usual default value is $E0hex/224dec for the character set in ROM at $E000hex/57344dec.

WSYNC $D40A Write

Wait For Horizontal Sync

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---|---|---|---|---|---|---|---|

| ? | ? | ? | ? | ? | ? | ? | ? |

This register allows programs to synchronize to the display. A write to this register halts the 6502 program through the end of the current scanline. This behavior is commonly used during Display List Interrupts to produce clean transitions/changes from one scanline to the next. The value written is unimportant.

VCOUNT $D40B Read

Vertical Line Counter

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---|---|---|---|---|---|---|---|

| ? | ? | ? | ? | ? | ? | ? | ? |

This register tracks the scan line currently being generated. The value returned is the actual scan line divided by 2. Blank lines generated at the start of the display are included. The value for NTSC will range from 0 to 130 for NTSC, and 0 to 155 for PAL. This value is useful during Display List Interrupts to identify the vertical screen position.

PENH $D40C Read

SHADOW: LPENH $0234

Light Pen Horizontal Position

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---|---|---|---|---|---|---|---|

| ? | ? | ? | ? | ? | ? | ? | ? |

This contains the horizontal color clock position when the light pen/light gun trigger is pressed. The shadow register is the recommended source for reading this information, since it will be updated during the vertical blank guaranteeing consistent and reliable results. Programs should avoid reading the hardware register directly unless the program is certain the register is read at a time insuring the value is valid. Light guns for the Atari function the same way as light pens with the addition of an optical magnifier allowing the screen to be read from a greater distance. The light pen/light gun input device requires a conventional CRT using a scanning electron beam. The light pen/light gun cannot work with modern LCD TVs and monitors.

PENV $D40D Read

SHADOW: LPENV $0235

Light Pen Vertical Position

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---|---|---|---|---|---|---|---|

| ? | ? | ? | ? | ? | ? | ? | ? |

This contains the VCOUNT value captured when the light pen/light gun trigger is pressed. The shadow register is the recommended source for reading this information, since it will be updated during the vertical blank guaranteeing consistent and reliable results. Programs should avoid reading the hardware register directly unless the program is certain the register is read at a time insuring the value is valid. Light guns for the Atari function the same way as light pens with the addition of an optical magnifier allowing the screen to be read from a greater distance. The light pen/light gun input device requires a conventional CRT using a scanning electron beam. The light pen/light gun cannot work with modern LCD TVs and monitors.

NMIEN $D40E Write

Non-Maskable Interrupt (NMI) Enable

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---|---|---|---|---|---|---|---|

| DLI | VBI | RESET | - | - | - | - | - |

NMIEN enables Non-Maskable Interrupts. The bit values:

| Feature | Bits Value | Description |

|---|---|---|

| Reset | $20 | Enable Reset key interrupt |

| VBI | $40 | Enable Vertical Blank Interrupt |

| DLI | $80 | Enable Display List Interrupt |

The Operation System sets NMIEN to the default $40hex/64dec during the power up routines. The NMI service routines first vector through $FFFAhex/65530dec which determines the cause and then transfers control to the interrupt service routine.

DLI:

If NMIEN's DLI bit is set when ANTIC encounters a Display List instruction with the DLI modifier bit set, then ANTIC triggers the DLI on the last scan line of that Display List instruction mode line.

The Operating System does not use DLIs, so the default address for the DLI vector (VDSLST, $0200hex/512dec) points to an RTI instruction in ROM. The application using DLIs must alter VDSLST to point to the desired DLI routine before enabling the DLI.

The 6502 Accumulator, X and Y register contents are not preserved before entry to the DLI routine. It is the responsibility of the DLI routine to save the state of the registers that will be used during the DLI routine, and then the last action is to restore the original values of the registers before exiting with an RTI instruction. Routines typically push the register values to the 6502 stack.

If multiple DLIs are used the first interrupt updates VDSLST to point to the address of the next interrupt, and so on for subsequent interrupts. The last Display List Interrupt routine on the screen points VDSLST back to the address of the first Display List Interrupt. Alternatively, a Vertical Blank Interrupt routine can be used to reset the VDSLST address to guarantee the DLIs remain in sync with the screen.

VBI:

When NMIEN's VBI bit is set, ANTIC will signals a Vertical Blank Interrupt at the end of processing the JVB (Jump vertical blank) at the end of the Display List. The Operating System uses the Vertical Blank to perform various housekeeping chores (among other things - updating timers, copying controller input values to their Shadow registers, and copying the contents of Shadow registers to the custom chips hardware registers.)

The OS jumps through VVBLKI ($0222hex/546dec) to begin the OS VBI Service Routine, and the OS VBI Routine exits with a jump through VVBLKD ($0224hex/548dec). By default VVBLKI points to the OS jump vector SYSVBV ($E45Fhex/58463dec) to begin the Vertical Blank Interrupt, and VVBLKD points to the OS jump vector XITVBV ($E462hex/58466dec).

User programs can insert execution of custom code either before (Immediate) or after (Deferred) the Operating System's Vertical Blank Interrupt routines. Since the OS Vertical Blank interrupt could be called while a user program is updating the vectors, the Operating system provides a routine, SETVBV ($E45Chex/58460dec), that will safely update the VVBLKI or VVBLKD vectors to point to a new routine:

- To set a new jump target for VVBLKI (Immediate) set the Y register to the low byte of the target address, the X register to the high byte of the target address, and the Accumulator to 6, then JSR SETVBV. The user code called through VVBLKI simply needs to exit by jumping to the OS Vertical Blank with a JMP SYSVBV ($E45Fhex/58463dec).

- To set a new jump target for VVBLKD (Deferred) set the Y register to the low byte of the target address, the X register to the high byte of the target address, and the Accumulator to 7, then JSR SETVBV.. The user code called through VVBLKD must exit by jumping to the OS Vertical Blank exit routine with a JMP XITVBV ($E462hex/58466dec).

When the CRITIC flag ($42hex/66dec) is non-zero execution of the Deferred Vertical Blank interrupt is suppressed regardless of the addresses in the vectors. The default value of CRITIC, 0, allows execution of both Immediate and Deferred Vertical Blank Interrupts.

NMIRES $D40F Write

Non-Maskable Interrupt (NMI) Reset

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---|---|---|---|---|---|---|---|

| ? | ? | ? | ? | ? | ? | ? | ? |

Any value written to NMIRES resets the bits in NMIST which indicate the reason for the most recent Non-Maskable Interrupt. This is used by interrupt dispatch code in the Operating System and there would ordinarily not be a reason for a user program to write here.

NMIST $D40F Read

Non-Maskable Interrupt (NMI) Status

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---|---|---|---|---|---|---|---|

| DLI | VBI | RESET | - | - | - | - | - |

The Operating System's Non-Maskable Interrupt dispatch routine reads this register to determine the reason for the interrupt and so which service routine to execute.

The bit values:

- $20 - Reset key interrupt

- $40 - Vertical Blank Interrupt

- $80 - Display List Interrupt

Display list

The display list is the list of instructions directing ANTIC how to generate the display. The data processed by this Display List "program" is the screen memory. The output is the graphics display. The kinds of graphics in the output (text vs addressable pixels) is determined by the instructions in the Display List.

The display List and the display data are written into RAM by the CPU. ANTIC reads the display List instructions, screen memory, and character set information from RAM using a technique known as direct memory access (DMA). A BASIC or 6502 machine language program's job is to initialize the display—set up the display List instructions, organize screen memory (and character set if applicable), and then direct ANTIC to start the display. After this, ANTIC automatically takes care of generating the screen display. This allows the Atari 8-bit computers to produce complex, mixed-mode displays without direct CPU intervention. Other platforms, even those designed much later, cannot either mix graphics modes in one display, or do so without complex CPU interrupts.

ANTIC processes the instructions in the display List, reads the screen memory (and character set data if applicable), translates this information into a real-time stream of graphics data, and sends this data stream to the CTIA/GTIA chip which applies the color to the graphics pixels and outputs the video. Together the two chips provide 6 text and 8 graphics modes (14 total). The more advanced version, GTIA, adds three alternative color interpretations for each ANTIC graphics mode providing a total of 56 (14 times four) graphics modes. However, only the ANTIC graphics modes based on half-color clock pixels are capable of expressing the complete color palette provided by the new color interpretations, and of those modes the ones convenient for use are ANTIC modes 2 (OS Graphics mode 0 text) and ANTIC mode F (OS Graphics mode 8). Thus the reasonable number of unique graphics modes available using the inherent hardware capabilities of ANTIC + CTIA/GTIA is 20–14 ANTIC modes + 3 additional color interpretations each for ANTIC modes 2 and F.

Display list instruction overview

The Atari display is built as a series of ANTIC instructions each describing a line of text or graphics mode progressively from the top to the bottom of the screen until the desired display area is filled. In effect, the screen is a vertical stack of ANTIC mode instructions. Different modes occupy different numbers of scan lines and use different amounts of RAM. Designing a display requires counting the scan lines of each Mode instruction and tracking the memory for each Mode line to prevent overrunning ANTIC or video standard limitations. (See the Limitations section).

Mixing multiple graphics modes in one display is done simply by providing different character or map mode instructions for the desired position on screen. For example, the Atari Operating System graphics modes 1 through 8 offer full screen display, or an option for a four-line text window at the bottom of the screen. This split screen feature is accomplished using the inherent capabilities of ANTIC and its Display List without any CPU interrupts or custom manipulation of the video hardware.

ANTIC has four types of instructions:

- Blank line - 8 instructions to display from 1 through 8 horizontal blank lines

- Jump instructions - 2 kinds of Jump instructions which reload ANTIC's program counter (3-byte instructions)

- Character mode - 6 instructions to display character data

- Map mode - 8 instructions to display colored pixels

Map and Character mode instructions have additional modifiers that can be enabled with the instruction:

- Horizontal scrolling - Enables horizontal fine scrolling

- Vertical scrolling - Enables vertical fine scrolling

- Load Memory Scan (LMS) - Sets the starting address of graphics/character data (3-byte instruction)

- DLI - Display List Interrupt (called "raster interrupt" or "Horizontal Blank Interrupt" on other systems)

Instruction Execution

ANTIC begins executing the Display List pointed to by the 16-bit address in registers DLISTL/DLISTH ($D402-$D403hex/54274-54275dec). The address registers are incremented by ANTIC automatically as each instruction is executed. ANTIC can only update the lowest 10 bits of the address during the automatic increment limiting the display list to begin and end within a 1K address range.

The registers are also updated during Display List execution by ANTIC's JMP (Jump) and JVB (Jump and wait for Vertical Blank). These instructions load the full 16-bits of address, so can be used to circumvent the 1K Display List limitation.

The address is also updated by the Operating System's Vertical Blank Interrupt (VBI) routine using the values from Operation System shadow registers SDLSTL/SDLSTH ($0230-$0231hex/560-561dec). When the OS VBI routine is enabled direct updates to the ANTIC DLIST registers by the CPU or the ANTIC Jump instructions will be overwritten by the OS during the next Vertical Blank. Since VBI processing is the usual state of the system, most programs rely on this and only update the OS shadow registers (SDLSTL/SDLSTH $0230-$0231hex/560-561dec) to set the Display List.

Instruction Bytes

This legend applies to the instruction bit diagrams below:

| Bit Value | Description |

|---|---|

| 0 | Bit must be 0 |

| 1 | Bit must be 1 |

| ? | Bit may be either 0 or 1, and is used for a purpose. |

| — | Bit is unused, or should not be expected to be a certain value |

| label | Refer to a later explanation for the purpose of the bit. |

Instruction Bits:

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---|---|---|---|---|---|---|---|

| DLI | LMS | VS | HS | Mode | Mode | Mode | Mode |

Bits 7:4 are modifiers for Playfield Mode instructions in bits 3:0. Bit value 1 Enables the modifier, and 0 disables the modifier.

- Bit 3:Bit 0 - Playfield Mode Instruction.

- Values $00, and $01 are special instructions.

- Mode values $02 through $0F specify Playfield Character and Map modes.

- Bit 4 - $10 - Horizontal Scroll.

- Bit 5 - $20 - Vertical Scroll.

- Bit 6 - $40 - Load Memory Scan.

- Bit 7 - $80 - Display List Interrupt.

Mode 0 Instruction - Blank Lines

| DLI | Lines | Lines | Lines | Mode | Mode | Mode | Mode |

|---|---|---|---|---|---|---|---|

| ? | ? | ? | ? | 0 | 0 | 0 | 0 |

When Mode bits are all zero ANTIC performs no playfield DMA and displays one or more blank scan line(s) of the background color. For normal color interpretation modes the "background" is color register COLBK (D01Ahex/53274dec) OS Shadow COLOR4 (02C8hex/712dec), though this differs for the GTIA color interpretation modes. See discussion of COLBK on the GTIA page for more information.

The number of blank scan lines are specified by the value of Bits 4 through Bits 6 allowing a range from 0 through 7. ANTIC adds one to this value and displays the resulting number of scan lines. Instruction Values:

| ANTIC Instruction | Scan Lines |

|---|---|

| 00hex/0dec | 1 blank scan line. |

| 10hex/16dec | 2 blank scan lines. |

| 20hex/32dec | 3 blank scan lines. |

| 30hex/48dec | 4 blank scan lines. |

| 40hex/64dec | 5 blank scan lines. |

| 50hex/80dec | 6 blank scan lines. |

| 60hex/96dec | 7 blank scan lines. |

| 70hex/112dec | 8 blank scan lines. |

Blank lines are useful for delaying the start of the screen display until the electron beam has left the vertical overscan area at the top of the display. The Atari Operating System creates all its graphics modes beginning with three 70hex/112dec instructions (or 24 blank scan lines) for this purpose. Blank lines are also useful for partitioning parts of a custom display with different purposes (i.e. a border between a status display and the main graphics.)

Blank Mode lines cannot be contained within a scrolling region, because Blank Mode line instructions inherently do not have Fine Scrolling Modifier bits. However, a Blank Mode instruction can be used to end a vertical scrolling region and is still subject to the expected scan line height changes per the vertical scroll value.

The DLI modifier bit is available for blank line instructions. When the DLI bit is enabled a Display List Interrupt will be triggered during the last blank scan line of the instruction. Since playfield DMA does not occur during blank lines (only Display list DMA and Player/Missile DMA (if enabled) occurs) the blank lines can be used where Playfield graphics will not be needed giving more time for Display List Interrupt routines changing color registers or Player/Missile positions.

Mode 1 Instruction - Jump

| DLI | LMS | VS | HS | Mode | Mode | Mode | Mode |

|---|---|---|---|---|---|---|---|

| 0 | ? | 0 | 0 | 0 | 0 | 0 | 1 |

When Mode value is 1 ANTIC executes a Jump in its program (the Display List). The next two bytes in the Display List are loaded into ANTIC registers DLISTL/DLISTH ($D402-$D403hex/54274-54275dec) changing the execution point of the next instruction.

There are two kinds of Jumps:

- 01hex/1dec JMP - Jump to address. This is used to load a new execution address in the middle of Display List execution, typically when the Display List must cross over a 1K boundary.

- 41hex/65dec JVB - Jump to address and wait for Vertical Blank. (JMP + LMS bit set) This is used to end the Display List. The address used should be the starting address of the Display List.

The DLIST registers are also updated by the Operating System's Vertical Blank Interrupt (VBI) routine using the values in shadow registers SDLSTL/SDLSTH (0230-0231hex/560-561dec). When the OS VBI routine is enabled direct updates to the ANTIC DLIST registers by the CPU or the ANTIC Jump instructions will be overwritten by the OS during the next Vertical Blank. This implies that an ANTIC JVB (Jump and wait for Vertical Blank) instruction that specifies an invalid address (or a valid address that differs from the shadow SDLST value) has no real effect on the display.

The JVB's argument usually points to the beginning of the same Display List, but it can also point to another Display List, so that a chain of Display Lists is executed after consecutive vertical blanks. Of course, to give ANTIC control over the start of the next Display List the OS Vertical Blank interrupt must be disabled to prevent it overwriting ANTIC hardware registers with the shadow register values.

Modes 2 to F Instructions - Playfield Character and Map Modes

| DLI | LMS | VS | HS | Mode | Mode | Mode | Mode |

|---|---|---|---|---|---|---|---|

| ? | ? | ? | ? | ? | ? | ? | ? |

The following is the list of ANTIC graphics mode instructions. For more detailed descriptions of each Mode see the Playfield Graphics Modes section.

| ANTIC Instruction | Mode Type | Bytes Per Mode Line (narrow/normal/wide) | TV Scan Lines per Mode Line | Color |

|---|---|---|---|---|

| 2 | Character | 32/40/48 | 8 | 1.5 |

| 3 | Character | 32/40/48 | 10 | 1.5 |

| 4 | Character | 32/40/48 | 8 | 5 (multi-color) |

| 5 | Character | 32/40/48 | 16 | 5 (multi-color) |

| 6 | Character | 16/20/24 | 8 | 5 (single-color) |

| 7 | Character | 16/20/24 | 16 | 5 (single-color) |

| 8 | Map | 8/10/12 | 8 | 4 |

| 9 | Map | 8/10/12 | 4 | 2 |

| A | Map | 16/20/24 | 4 | 4 |

| B | Map | 16/20/24 | 2 | 2 |

| C | Map | 16/20/24 | 1 | 2 |

| D | Map | 32/40/48 | 2 | 4 |

| E | Map | 32/40/48 | 1 | 4 |

| F | Map | 32/40/48 | 1 | 1.5 |

The memory requirement for a Mode Line is determined by two factors:

- The width bits set in the DMACTL hardware register.

- The presence of the Horizontal Fine Scroll Display List Instruction Modifier.

The Horizontal Fine Scroll Modifier will change the memory requirement for the current Mode Line from the DMACTL-specified width to the next largest value.

Instruction Modifiers

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---|---|---|---|---|---|---|---|

| DLI | LMS | VS | HS | ? | ? | ? | ? |

Bits 7:4 are modifiers for Playfield Mode instructions in bits 3:0. Playfield Mode Instruction values range from $02 to $0F. Modifier bit value 1 Enables the modifier, and 0 disables the modifier.

- Bit 4 - $10hex/16dec Horizontal Scroll.

- Bit 5 - $20hex/32dec Vertical Scroll.

- Bit 6 - $40hex/64dec Load Memory Scan.

- Bit 7 - $80hex/128dec Display List Interrupt.

HS Modifer - Horizontal Fine Scroll

Bit4: position value $10, controls horizontal scrolling of the playfield mode.

When horizontal scrolling is enabled ANTIC retrieves more screen memory bytes than displayed in order to show partially scrolled display bytes at the beginning and end of the line. If the display is in Narrow mode ANTIC retrieves the number of screen bytes necessary for Normal mode. If the display is in Normal mode ANTIC retrieves the number of bytes needed for Wide screen mode. In Wide screen mode ANTIC does not retrieve any additional screen bytes. Scrolling in Wide screen will cause blank data to be shifted into the scrolled area. This is not a problem, because it occurs in the overscan area which is not visible on a normal NTSC/PAL display.

VS Modifer - Vertical Fine Scroll

Bit5: position value $20, controls vertical scrolling of the Playfield mode.

The Vertical scrolling region in a display is defined by setting the VS bit ($20) on a sequential series of ANTIC Mode Lines in the Display List. The first Mode line without the VS bit set becomes the end of the scrolling region and is used as a buffer line to supply the new information to scroll up into the bottom of the scrolling region.

LMS Modifer - Load Memory Scan

Bit6: position value $40, loads a new address for the start of screen memory for the current Playfield mode line.

The LMS option loads ANTIC's screen memory scan address with the 16-bit value in the two bytes following the instruction. The Character or Map mode specified will begin displaying bytes from that address. The LMS option must appear in the first Playfield Mode Instruction line (not Blank Line) in the Display List to initialize ANTIC to begin reading at the start of screen memory. Most of the Operating System-generated full screen modes will have only that one occurrence of the LMS modifier present in the Display List. ANTIC will automatically increment its LMS address at the end of each mode line in preparation for the next line. As long as screen memory does not cross over a 4K boundary the LMS modifier is not needed on subsequent Playfield Mode Instructions.

Full screen displays using Playfield Map Modes E or F will have a second occurrence of the LMS modifier on a Map Instruction near the middle of the screen, since the full display requires more than 4K of screen memory. (Mode F displays include high res 320 pixel lines, and the GTIA display modes.)

Combining the Map and Character Mode instructions with the LMS bit makes it possible to set the screen memory address freely within the 64K address space independently for each display line. In other words, the screen memory does not have to be completely contiguous memory scanned sequentially towards higher addresses - only that a single Mode line must be provided with adequate sequential bytes of memory to meet the requirements of that Mode, width of the display, and Scrolling feature.

DLI Modifer - Display List Interrupt

Bit7: position value $80, directs ANTIC to invoke a CPU-serviced interrupt on the last scan line of the Playfield Mode.

If ANTIC register NMIEN (D40Ehex/54286dec) has Bit7 ($80) set then on the last scanline of the Mode line an interrupt routine will be triggered which is vectored through address VDSLST (200hex/512dec).

The 6502 Accumulator, X and Y register contents are not preserved before entry to the DLI routine. It is the responsibility of the DLI routine to save the state of the registers used during the DLI, and then restore the original values of the registers before exiting with an RTI instruction. Routines typically push the register values to the 6502 stack.

DLI routines are ordinarily short and quick, changing the color registers or Player-Missile positions before exiting. However, brevity is not required. As long as the DLI routine exits before the start of the next DLI routine the DLI routine can continue updating values across multiple scanlines.

Playfield Graphics Modes

The ANTIC chip allows a variety of different Playfield modes and widths. However, the original Atari Operating System included with the Atari 800/400 computers provides easy access to a limited subset of these graphics modes. ANTIC Playfield modes are exposed to users through Atari BASIC via the "GRAPHICS" command, and to some other languages, via similar system calls. Oddly, the modes not directly supported by the original OS and BASIC are modes most useful for games. The later version of the OS used in the Atari 8-bit XL/XE computers added support for most of these "missing" graphics modes.

The ANTIC chip uses a Display List and other settings to create these modes. Any graphics mode in the default GTIA color interpretation can be freely mixed without CPU intervention by changing instructions in the Display List.

The ANTIC screen geometry is not fixed. A hardware register can direct ANTIC to display narrow playfield (128 color clocks/256 hi-res pixels wide), normal width playfield (160 color clocks/320 hi-res pixels wide), and wide, overscan playfield (192 color clocks/384 hi-res pixels wide). While the Operating System's default height for graphics modes is 192 scan lines Antic can display vertical overscan up to 240 TV scan lines tall by creating a custom Display List.

Mode F produces colors through NTSC artifacting and works in a similar manner to the Apple II's graphics modes. The pixel resolution is 320 across but the color resolution half that, thus each group of two pixels will "blend" together to form a single color and four artifact colors may be generated this way. They will be tinted if the foreground and background color are set to something other than black/white/gray. The exact colors produced this way vary with different Atari 8-bit models and also between the CTIA and GTIA chips, thus undesirable artifact colors may result from running software that uses Mode F on a machine other than the one it was developed for. It was not possible to obtain artifact coloring on PAL machines and Mode F will be monochrome on them.

Mode F was not widely used by software due to its high memory requirements (8k) and inconsistent artifact colors that did not appear the same on every model of Atari 8-bit computer. Games that utilize it include Sierra graphical adventures such as Troll's Tale and Wizard and the Princess, Lode Runner, and the Ultima series.

The video display system was designed with careful consideration of NTSC display methods and limitations. The system CPU clock and video hardware are synchronized to one-half the NTSC clock frequency. Consequently, the pixel output of all display modes is based on the size of the NTSC color clock which is the minimum time needed to guarantee correct and consistent color regardless of the pixel's horizontal location on the screen. The result is accurate pixel size and coloring that does not display color "strobing" defects when horizontally scrolled. (Color strobing is unsightly hue changes in pixels based on horizontal position which is caused when signal changes do not align with the color clock and so do not provide the TV/monitor hardware adequate time to reach the correct color.)

Character Modes

| Antic Text Mode | OS mode | Characters (or Bytes) Per Mode Line (narrow/normal/wide) | TV Scan Lines per Mode Line | Colors | Colors per Character Matrix | Characters in Font | Matrix Pixel Size (Color Clocks x Scan Lines) | Bits Per Matrix Pixel | Matrix Map (Color Clocks x Scan Lines) | Matrix Map (Pixels x Pixels) | Notes |

|---|---|---|---|---|---|---|---|---|---|---|---|

| 2 | 0 | 32/40/48 | 8 | 1.5 | 1 | 128 | 1/2 x 1 | 1 | 4 x 8 | 8 x 8 | High-res pixels. When the high bit of character is set (values $80 to $FF) the character data is displayed per the CHACTL setting. |

| 3 | N/A | 32/40/48 | 10 | 1.5 | 1 | 128 | 1/2 x 1 | 1 | 4 x 8/10 | 8 x 8 | High-res pixels. Lowercase characters are displayed 2 scan lines lower allowing descenders. |

| 4 | 12 (XL OS) | 32/40/48 | 8 | 5 | 4 | 128 | 1 x 1 | 2 | 4 x 8 | 4 x 8 | Two bits per pixel allowing 4 colors inside one character matrix. When the high bit of the character is set a fifth color replaces one of the other four. |

| 5 | 13 (XL OS) | 32/40/48 | 16 | 5 | 4 | 128 | 1 x 2 | 2 | 4 x 16 | 4 x 8 | Color same as above Antic Mode 4. Characters are twice as tall. |

| 6 | 1 | 16/20/24 | 8 | 5 | 1 | 64 | 1 x 1 | 1 | 8 x 8 | 8 x 8 | One color per character matrix. The characters in each 64 character block are shown in a different color. When the high bit of the character is set a fifth color replaces one of the other four. |

| 7 | 2 | 16/20/24 | 16 | 5 | 1 | 64 | 1 x 2 | 1 | 8 x 16 | 8 x 8 | Color same as above Antic Mode 6. Characters are twice as tall. |

Glyph Rendering

All character sets use 8 sequential bytes to represent the character. Four types of character/glyph rendering of those bytes are available. Each Character Mode is associated to a specific rendering method:

- Standard: ANTIC Mode 2. Based on the high resolution graphics modes each bit in the character glyph represents one pixel on screen that is 1/2 color clock wide. The background color is COLPF2 rather than COLBK used in other Character and Map modes. COLBK appears as a border around all four sides of the Playfield. 0 value bits in the character glyph show the background color. 1 value bits show the luminance value from COLPF1 based on the background (COLPF2) color. The character set uses 128 characters and requires 1024 bytes of RAM.

- Descenders: ANTIC Mode 3. A modification of the Standard method. The method of pixel color display is the same. Each mode line is 10 scanlines tall, though the character glyph is still 8 bytes. Characters 00hex/0dec to 5Fhex/95dec display in the top 8 scan lines with two blank scan lines added at the bottom. Characters 60hex/96dec to 7Fhex/127dec begin with two blank scan lines at the top, and then display the glyph bytes in the bottom 8 scan lines. The first two bytes in the glyph are moved to the bottom two scan lines. This allows a properly designed character set to display true descenders. The character set uses 128 characters and requires 1024 bytes of RAM.

- Single Color: ANTIC Modes 6 and 7. In these modes each bit in the character glyph represents one pixel that is one color clock wide. The background color is COLBK. Characters may be displayed in a choice of one of four colors. The six low bits of the character value identifies the glyph and the two high bits identify a color. Since the character value is reduced to six bits the character set uses 64 characters and requires 512 bytes of RAM. 0 value bits in the character glyph show the background color. 1 value bits in the glyph data shows one of four possible color choices based on the two high bits of the character value. Character value bits 7 and 6:

| Character bits [7:6] | Character Range | Color of Glyph pixels |

|---|---|---|

| 0 0 = $00 | $00 – $3F | COLPF0 |

| 0 1 = $40 | $40 – $7F | COLPF1 |

| 1 0 = $80 | $80 - $BF | COLPF2 |

| 1 1 = $C0 | $C0 - $FF | COLPF3 |

- Multi-Color: ANTIC Modes 4 and 5. In these character modes each pair of bits in the character glyph represents a pixel one color clock wide, thus a single byte of glyph information represents 4 pixels rather than the 8 pixels of other modes. The character set uses 128 characters and requires 1024 bytes of RAM. The background color is COLBK. This mode allows up to four colors (including the background) to be displayed in one character matrix. If the high bit of the character value is set (i.e. inverse video) then a fifth color, COLPF3, is displayed in place of the pixel bit pattern "11" that ordinarily shows COLPF2. The color choices based on the bit pairs of the character glyph:

| Character bit 7 | Glyph bit pair | Color of Glyph pixel |

|---|---|---|

| 0/1 = $00/$80 | 0 0 | COLBK |

| 0/1 = $00/$80 | 0 1 | COLPF0 |

| 0/1 = $00/$80 | 1 0 | COLPF1 |

| 0 = $00 | 1 1 | COLPF2 |

| 1 = $80 | 1 1 | COLPF3 |

Map Modes

| Antic Map Mode | OS Mode | Pixels Per Mode Line (narrow/normal/wide) | TV Scan Lines per Mode Line | Bytes per Mode Line (narrow/normal/wide) | Bits per Pixel | Colors | Color Clocks per Pixel |

|---|---|---|---|---|---|---|---|

| 8 | 3 | 32/40/48 | 8 | 8/10/12 | 2 | 4 | 4 |

| 9 | 4 | 64/80/96 | 4 | 8/10/12 | 1 | 2 | 2 |

| A | 5 | 64/80/96 | 4 | 16/20/24 | 2 | 4 | 2 |

| B | 6 | 128/160/192 | 2 | 16/20/24 | 1 | 2 | 1 |

| C | 14 (XL OS) | 128/160/192 | 1 | 16/20/24 | 1 | 2 | 1 |

| D | 7 | 128/160/192 | 2 | 32/40/48 | 2 | 4 | 1 |

| E | 15 (XL OS) | 128/160/192 | 1 | 32/40/48 | 2 | 4 | 1 |

| F | 8 | 256/320/384 | 1 | 32/40/48 | 1 | 11⁄2 | 1⁄2 |

GTIA Modes

GTIA modes are Antic Mode F displays with an alternate color interpretation option enabled via GTIA register PRIOR ($D01Bhex/53275dec) shadowed by GPRIOR ($026Fhex/623dec). The full color expression of these GTIA modes can also be engaged in Antic text modes 2 and 3, though these will also require a custom character set to achieve practical use of the colors. See GTIA for more information.

| Antic Map Mode | OS Mode | Pixels Per Mode Line (narrow/normal/wide) | TV Scan Lines per Mode Line | Bytes per Mode Line (narrow/normal/wide) | Bits Per Pixel | Colors | Color Clocks per Pixel | Notes |

|---|---|---|---|---|---|---|---|---|

| F | 9 | 64/80/96 | 1 | 32/40/48 | 4 | 16* | 2 | 16 shades of the background color. |

| F | 10 | 64/80/96 | 1 | 32/40/48 | 4 | 9 | 2 | pixel indirection mode—uses all 9 Playfield and Player/Missile color registers for pixels. |

| F | 11 | 64/80/96 | 1 | 32/40/48 | 4 | 16* | 2 | 15 color hues all in the same luminance set by the background, plus the background color. |

Scrolling

Before video displays became a common part of the user interface many computers used a teletype—a printer usually with continuously-fed paper. User input and the computer generated output were printed on the paper fed through the printer. This widely understood interface for user input and computer output continued with the introduction of video displays as computers presented a metaphor of the screen as a view port over an imagined, infinite roll of paper. Information is displayed on screen beginning at the top until it reaches the bottom of the screen and when the computer needs to introduce new information it shifts all the screen information up providing an empty space at the bottom for the new information and consequently erasing the topmost information.

This kind of scrolling is called, "coarse scrolling". It is achieved by moving bytes of memory through a designated screen display area. Moving a kilobyte (or more) of memory is CPU intensive and slower computers may not be able to accomplish anything else while updating screen data. As a means of animating a display the results can be jerky when the CPU cannot update the screen memory faster than the display hardware reads the memory to generate the video output. Motion fluidity is impaired, since the minimum amount of shifting the display is the size of an entire character. Most computers including the Atari 8-bits accomplish coarse scrolling as described above — common examples are viewing a long BASIC program listing or directory of files.

Coarse scrolling implemented by bulk movement of data is often the only method of scrolling possible on most computers. However, ANTIC provides direct hardware support for vertical and horizontal, coarse and fine scrolling taking the concept of a "view port moving over data" from a metaphorical illusion to literal implementation. These ANTIC features deliver rapid, smooth, full screen movement requiring negligible CPU time and so free the CPU for other work.

All ANTIC display modes, Text and Map modes, can exercise the hardware scrolling features.

Vertical Coarse Scrolling

Vertical coarse scrolling is the easiest feature to exercise. The first Text or Map Mode instruction in every Display List always includes the LMS instruction modifier specifying the start of screen memory. As it generates the display, ANTIC automatically increments its memory scan pointer from Mode line to Mode line to display memory contiguously. Therefore, a display can be "moved" by merely updating the initial LMS modifier's address; adding the number of bytes used for a line in the current Text or Map Mode shifts the screen contents up one line while subtracting the same amount moves the screen down. So, the display is actually a view port that is moved to look at a different areas of memory rather than moving the memory into a fixed screen map.

Since ANTIC's memory scan counter cannot automatically increment over a 4K boundary the limit of vertical scrolling in this simple manner is up to 4K of movement. A full screen of Mode 2 text using approximately 1K can continuously scroll the height of four screens until reaching the 4K boundary. Likewise, a Mode 7 text display can scroll the height of 16 entire screens.

Naturally, that trivial example is of limited usefulness. Many scrolling implementations scroll only part of the screen while other sections remain fixed. This problem is solved by the inherent capabilities of the ANTIC Display List. In this situation the Display List would add Mode instructions using LMS modifiers on the first mode line of the screen sections that should not move which effectively locks these parts of the display while the LMS modifier address for the scrolling section is updated.

Further enhancement of this concept uses the LMS modifier option on every line that does scroll. Vertical scrolling on this display requires updating one LMS modifier address for each Mode line in the scrolling region. When the display is managed at this level of detail ANTIC's 4K screen RAM boundary can be easily circumvented. Even in this worst case example the CPU effort expended is a tiny fraction of the processing needed to bulk move screen data.

One other limit to be aware of is that the two byte LMS modifier address must not be updated when ANTIC is processing the LMS. If ANTIC reads the LMS address while it is partially updated ANTIC will display the incorrect section of memory for that Mode line. When the scrolling region of a display requires multiple LMS address updates the possibility of a partial update increases, and the possibility of having two subsequent lines display the same data also increases. Programs solve this in a number of ways—performing updates during the Vertical blank, monitoring the VCOUNT before updates, or doing the updates in Display List Interrupts executed during sections of the display away from the scrolling region.

Vertical Fine Scrolling

Vertical Fine Scrolling allows single scan line movement of the scrolling region for Text and Map modes which are greater than one scan line tall. Vertical Fine Scrolling for Map modes only one scan line tall is logically not practical. The effect of vertical "fine" scrolling for single scan line Map modes can be performed using the easier coarse scrolling method.

Fine scrolling requires setup to define the scrolling region. This is done by setting the Vertical Scroll (VS) modifier bit in sequential Display List instructions. The first Mode line instruction without the VS bit set becomes the end of the scrolling region and is used as a buffer line to supply the new scan lines to scroll up into the bottom of the scrolling region.

ANTIC's process of vertical fine scrolling works by simply directing ANTIC to skip a number of scan lines for the first mode line of the scrolling region. Subsequent Mode lines in the scrolling region are not affected. The last line of the region supplies the bottom border of the scrolling region displaying the number of scan lines that were removed from the first line. This number of scan lines is controlled with the VSCROL register. The value ranges from 0 to the ANTIC Mode line's scan line height - 1. The maximum value range covers fine scrolling 16 scan lines from 0 to 15.

When the fine scrolling limit is reached, scrolling continues by resetting the VSCROL value and performing a coarse vertical scroll of the scrolling region.

Horizontal Coarse Scrolling

Horizontal coarse scrolling requires a little more effort than vertical scrolling. While horizontal scrolling is expected to present the illusion of a view port moving left and right across a wide panoramic scene made of screen memory, ANTIC's automatic memory scan increment conflicts with this idea that the rows of screen data is wider than the display. Presenting screen memory as long horizontal lines requires an LMS modifier for every Display List Text or Map Mode instruction in the scrolling region. A horizontal step is accomplished by incrementing or decrementing all the LMS addresses of the scrolling region.

Horizontal scrolling requires the same Display List implementation as the worst case example described for Vertical Coarse Scrolling. So, where Horizontal scrolling is implemented, vertical scrolling is also supported just by changing the value incrementing or decrementing the LMS addresses. The other benefit of this arrangement is that it is easy to manage screen memory around ANTIC's 4K screen memory boundary limit.

See the Vertical Coarse Scrolling section for further discussion and time constraints when updating LMS modifier addresses.

Horizontal Fine Scrolling

Horizontal Fine Scrolling allows single color clock movement of the scrolling region for Text and Map modes. For all normal color interpretations this is by color clock, not pixel even when pixels are larger (or smaller) than the color clocks. ANTIC Modes using the alternate GTIA color interpretations must be scrolled by an entire GTIA pixel (two color clocks). Only even values should be used to ensure correct GTIA pixel scrolling. Odd values of HSCROL will shift the GTIA pixel stream into a different state that will be interpreted as different colors.

Fine scrolling requires setup to define the horizontal scrolling region. The first step is to start with a Display List using the LMS instruction modifier to specify starting address of each Mode line. This is done to organize screen memory as long rows of data for the display. The next step is setting the Horizontal Scroll (HS) modifier bit in all Display List Mode line instructions for the scrolling region.

This number of color clocks to shift is controlled with the HSCROL register. The maximum HSCROL value range covers fine scrolling 16 color clocks from 0 to 15. The color clock information used is buffered from the beginning of the mode line (ANTIC's current memory scan pointer) using enough screen memory bytes to satisfy the 16 color clocks. Horizontal scrolling simply directs ANTIC how many color clocks it can output from the buffered 16 color clocks starting at the last (right most) color clock of the buffered memory. Zero (0) is no color clocks output from the buffer. 1 is the last (right most) color clock of the buffer. The color clocks are inserted at the left edge of the screen, causing the scrolling area of the screen to shift to the right.

When the fine scrolling limit is reached, continue scrolling by resetting the HSCROL value and performing a coarse horizontal scroll of the scrolling region. ANTIC's 16 color clock range permits fine scrolling multiple Text Mode characters or more than one byte worth of Map mode pixels. Therefore, the update to the LMS addresses may add or subtract multiple bytes.

Alternate Scrolling Methods

An interesting use of ANTIC's DMA memory scan behavior permits a strategy for apparently long horizontal scrolling distances, but uses a fraction of the real memory required. As discussed in Horizontal Coarse Scrolling ANTIC's automatic memory scan increment from Mode line to Mode line conflicts with the idea that the rows of screen data are wider than the display. Using memory actually organized as a long, horizontal, contiguous series of bytes requires an LMS modifier for every Display List Text or Map Mode instruction in the scrolling region.

Instead of using an LMS modifier for every line this method uses a more "normal" display list that only requires one LMS modifier at the start of the scrolling region. An increment (+1) to the LMS modifier address makes the scrolling region appear to move toward the left. However, the "new" information that has moved into the right side of the scrolling region was previously the first byte on the following line (except for the last byte of the last line — that information had been completely off screen).

The second half of this strategy requires the last byte/character of every line in the scrolling region to be updated to show the desired, new information. For a typical scrolling display this would mean updating the last byte of one or two dozen lines which takes a trivial amount of time in assembly. So, if this scrolling process involves a full screen Mode 2 or Mode 4 text display (rather worst case) and uses the entire 4K capability of ANTIC's automatic screen memory addressing, then the horizontal scrolling can continue in this manner for about 3,000 steps; equivalent to 75 full screens.

However, even the 4K memory use is not required. After all the data from the first full screen has been shifted off the display the scrolling application can rebuild the first screen to contain a known transition point so that the scrolling action can jump back to the first address in the block with no apparent stutter or obvious interruption in the scrolling.

Fine scrolling this arrangement requires a little more planning. When fine scrolling is enabled in the Display List ANTIC retrieves more information than the Mode line requires for display. As each mode line now uses more memory, the new information scrolled into the side of the display is not the byte/character that was displayed at the start of the next line. However, this does not impair the scrolling process and merely changes the value of addition and subtraction used to locate the start and end of each display line.

Display List Interrupts (DLI)

ANTIC includes a feature to trigger a CPU-serviced interrupt at specific vertical positions on the screen. This is built into the ANTIC Display List which directs ANTIC to launch the interrupt during the last scan line of the current Mode instruction, and so is called "Display List Interrupt". Other platforms call this activity, "Raster interrupts", or "Horizontal blank interrupts". The usual purpose is to change display-related values at a known location so transitions are visually precise or occur where they will not conflict with display activity. Possibilities include, but are not limited to changing color register values, Player/Missile horizontal positions, and fine scrolling values. Since the DLI is 6502 machine code executed by the CPU, any kind of processing work is possible provided it is short enough to not conflict with other activity and does not overrun a subsequent Display List Interrupt. A good example is mouse controller polling which must be done more frequently than 1/60th of a second.

Overview

Properly launching the interrupt requires the following conditions:

- A Display List with a Mode instruction that includes the Display List Interrupt (DLI) modifier bit set. (Bit 7 - $80hex/128dec)

- ANTIC's NMIEN register has the DLI bit set. (Bit 7 - $80hex/128dec)

- The Operating System vector for the Display List Interrupt (VDSLST, $0200hex/512dec) points to the starting address of the interrupt routine.

Proper Setup

When updating display control values care must be taken to ensure ANTIC is not currently using them. If ANTIC is processing the Display List containing an Instruction with the DLI modifier, then an interrupt could be dispatched while changing the VDSLST address, potentially crashing the system. If a Display List uses multiple interrupts, and interrupts are enabled in NMIEN after ANTIC has already passed Mode Instructions with DLI modifiers, then the Display List Interrupts will be started out of order, causing unexpected results.

A reasonable sequence of events to install a Display List using Display List Interrupts:

- Turn off ANTIC Display List Interrupts by clearing bit 7 ($80) of NMIEN by setting the register to value $40 which allows the Vertical Blank Interrupt to continue running.

- Turn off ANTIC Display List DMA. Turn off the DMA in the Shadow register first (SDMCTL), and then if desired the same can be done to the hardware register (DMACTL). Bit 5 (value $20) must be cleared, but most implementations would choose to zero all bits and then when the time comes to restart the screen restore the correct value of all bits.

- Set the Display List pointer Shadow address DLISTL/DLISTH to the starting address of the new Display List.

- Set the Display List Interrupt address VDSLST ($0200hex/512dec) to the starting address of the interrupt routine.

- Wait for the next Vertical Blank Interrupt (VBI) to apply the Shadow register changes. Possible methods:

- Monitor RTCLOCK ($12/$13/$14hex/18/19/20dec) for an increment indicating the VBI occurred.

- Monitor ANTIC's VCOUNT for changes indicating the next frame has started.

- Turn on ANTIC Display List Interrupts by setting bit 7 ($80) of NMIEN. The usual value for NMIEN is $C0 which enables DLI and VBI.

- Turn on ANTIC Display List DMA by updating the Shadow register (SDMCTL). Bit 5 (value $20) must be set, as should the bits for Playfield width, and if needed, the bits related to Player/Missile graphics.

A program tightly integrated with the display cycle and aware of the electron beam position relative to the current display can bypass turning off Display List DMA. Likewise, turning off the display is not needed if the setup occurs during the vertical blank.

Code Considerations

The 6502 Accumulator, X and Y register contents are not preserved before entry to the DLI routine. It is the responsibility of the DLI routine to save the state of the registers that will be used during the DLI routine, and then the last action is to restore the original values of the registers before exiting with an RTI instruction. Routines typically push the register values to the 6502 stack.

If multiple DLIs are used the first interrupt updates VDSLST to point to the address of the next interrupt, and so on for subsequent interrupts. The last Display List Interrupt routine on the screen points VDSLST back to the address of the first Display List Interrupt.

If a value changed by a DLI has an Operating System Shadow register and the Vertical Blank Interrupts are enabled, then the value in effect before (above) the screen position of the Display List Interrupt is the value of the Shadow, and the value after (below) the screen position is the value from the DLI (and any other DLI that later changes it.) If the value does not have an Operating System Shadow then there should be an initial DLI (or VBI) routine which sets a starting value.

If a graphics object is being displayed while the DLI changes its value the results may be inconsistent. The most common example is changing the background color. Since the DLI begins executing while the electron beam is in a visible portion of the screen, the transition from the previous background color to the new color written by the DLI will be visible somewhere on the current scan line. (The exact location varies based on DMA requirements for the display mode and Player/Missile graphics.) To produce a clean transition from scan line to scan line the code should first write to WSYNC which halts the DLI execution until the end of the scan line, and then write to the desired registers.

While the usual operation of the DLI is to change a few display-oriented values, and then return to the main code, this is not a requirement. It is safe for a DLI to run for several, or many scan lines as long as it exits before the next DLI or the Vertical Blank Interrupt.

Examples

A trivial example of a Display List Interrupt that changes the background color:

DLI

PHA ; Save Accumulator on stack

LDA #$9C ; Load light blue (color $9, luminance $C)

STA WSYNC ; Wait to sync to the end of the scanline

STA COLBK ; Set the background

PLA ; Restore Accumulator from stack

RTI ; The end.

Player/Missile Graphics

Most Player/Missile graphics functionality is in the domain of the CTIA/GTIA chip. CTIA/GTIA controls position, size, color, priority, and collision detection for Player/Missile graphics objects, but its actual shape rendering implementation goes no farther than a single byte pattern per object presented uniformly on all scan lines. (The patterns are set in CTIA/GTIA's GRAF* graphics pattern registers.) In the end, by itself CTIA/GTIA generates Player/Missile objects as only vertical stripe patterns on the screen.

ANTIC's design includes DMA capability so that it may read its Display List and Playfield graphics data. This direct memory access capability is leveraged to read data on behalf of CTIA/GTIA and update the GRAF* graphics pattern registers as each display scan line is generated. In this way ANTIC provides Player/Missile objects with patterns that vary over the height of the screen and so appear as traditional "sprite" graphics.

Bits 2 and 3 of ANTIC's DMACTL register (shadowed by SDMCTL) control ANTIC's retrieval of Player/Missile data to update CTIA/GTIA graphics pattern registers.

DMACTL Player/Missile DMA control bits values (bits [3:2]):

- $00 - Disable Player and Missile DMA

- $04 - Enable Missile DMA

- $08 - Enable Player DMA

- $0C - Enable Player and Missile DMA

Missile DMA can be enabled without player DMA. However, when Player DMA is enabled, Missile DMA automatically occurs to keep the DMA timing consistent, but the data is not delivered to the Missile's GRAFM register.

Bit 4 (value 10hex/16dec) of the DMACTL register controls the frequency of new data retrieval. ANTIC retrieves data and updates CTIA/GTIA every scan line. The DMACTL resolution settings affect how often ANTIC increments its internal DMA pointer for fetching new data. Single Line resolution Player/Missile graphics increments the DMA address every scan line, and Double Line resolution increments the DMA address with every even scan line. The DMACTL bit values for Player/Missile resolution:

- $00 - Double line resolution. New data is fetched by DMA on even scan lines, but an update to CTIA/GTIA Player/Missile Graphics pattern registers still occurs on every scan line. Consequently, each Player/Missile byte pattern is two scan lines tall. When Double line resolution is enabled CTIA/GTIA register VDELAY (D01Chex/53276dec) can be used to mask ANTIC's updates on even scan lines shifting the bit pattern of individual Players and Missiles down one scan line.

- $10 - Single line resolution. A new DMA fetch and Player/Missile register update occurs on every scan line. CTIA/GTIA register VDELAY (D01Chex/53276dec) masking the updates on even scan lines reduces Single line Player/Missile resolution to appear to be Double line resolution, though the data is shifted one scan line lower.

CTIA/GTIA must also be specifically enabled to receive the Player/Missile graphics data via DMA to correctly present the objects on screen. See CTIA/GTIA's GRACTL register for more information.

The location of memory read by ANTIC for Player/Missile graphics is controlled by register PMBASE. This value of PMBASE provides the starting page of the base address for Player/Missile graphics. When double line resolution P/M graphics are operating the PMBASE value must begin on a 1K boundary. When single line resolution P/M graphics are operating the PMBASE value must begin on a 2K boundary. The memory maps for the Player/Missile graphics modes:

Double line resolution (1 byte per 2 scanlines, 128 bytes each object) relative to PMBASE x 100hex/256dec:

| UNUSED | Missiles 3/2/1/0 | Player 0 | Player 1 | Player 2 | Player 3 | |

|---|---|---|---|---|---|---|

| Start/Top of Screen | ||||||

| dec | +0 | +384 | +512 | +640 | +768 | +896 |

| hex | +$00 | +$180 | +$200 | +$280 | +$300 | +$380 |

| End/Bottom of screen | ||||||

| dec | +383 | +511 | +639 | +767 | +895 | +1023 |

| hex | +$17F | +$1FF | +$27F | +$2FF | +$37F | +$3FF |

Single line resolution (1 byte per scanline, 256 bytes each object) relative to PMBASE x 100hex/256dec:

| UNUSED | Missiles 3/2/1/0 | Player 0 | Player 1 | Player 2 | Player 3 | |

|---|---|---|---|---|---|---|

| Start/Top of Screen | ||||||

| dec | +0 | +768 | +1024 | +1280 | +1536 | +1792 |

| hex | +$00 | +$300 | +$400 | +$500 | +$600 | +$700 |

| End/Bottom of screen | ||||||

| dec | +767 | +1023 | +1279 | +1535 | +1791 | +2047 |

| hex | +$2FF | +$3FF | +$4FF | +$5FF | +$6FF | +$7FF |

Missiles share the same bytes of the memory maps above, two bits per Missile:

| Missile | Bits | Value/Mask |

|---|---|---|

| 0 | ------11 | $03 |

| 1 | ----11-- | $0C |

| 2 | --11---- | $30 |

| 3 | 11------ | $C0 |