Software:Xilinx Vivado

| |

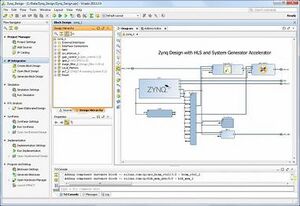

Xilinx Vivado Design Suite 2014.2 with Block Design panel (center) and project navigation tree (left) | |

| Developer(s) | Xilinx (AMD) |

|---|---|

| Initial release | April 2012[1] |

| Stable release | |

| Written in | C++ |

| Operating system | Microsoft Windows, Linux |

| Available in | English |

| Type | EDA |

| License | WebPACK Edition: no-cost for selected (smaller) devices[4] Other editions: commercial |

| Website | https://www.xilinx.com/products/design-tools/vivado.html |

Vivado Design Suite is a software suite produced by Xilinx for synthesis and analysis of hardware description language (HDL) designs, superseding Xilinx ISE with additional features for system on a chip development and high-level synthesis.[1][5][6][7] Vivado represents a ground-up rewrite and re-thinking of the entire design flow (compared to ISE).[8][9][10]

Like the later versions of ISE, Vivado includes the in-built logic simulator.[11] Vivado also introduces high-level synthesis, with a toolchain that converts C code into programmable logic.[6]

Replacing the 15 year old ISE with Vivado Design Suite took 1000 man-years and cost US$200 million.[12]

Features

Vivado was introduced in April 2012,[1] and is an integrated design environment (IDE) with system-to-IC level tools built on a shared scalable data model and a common debug environment. Vivado includes electronic system level (ESL) design tools for synthesizing and verifying C-based algorithmic IP; standards based packaging of both algorithmic and RTL IP for reuse; standards based IP stitching and systems integration of all types of system building blocks; and the verification of blocks and systems.[13] A free version WebPACK Edition of Vivado provides designers with a limited version of the design environment.[14]

Components

The Vivado High-Level Synthesis compiler enables C, C++ and SystemC programs to be directly targeted into Xilinx devices without the need to manually create RTL.[15][16][17] Vivado HLS is widely reviewed to increase developer productivity, and is confirmed to support C++ classes, templates, functions and operator overloading.[18][16] Vivado 2014.1 introduced support for automatically converting OpenCL kernels to IP for Xilinx devices.[19][16] OpenCL kernels are programs that execute across various CPU, GPU and FPGA platforms.[16][19]

The Vivado Simulator is a component of the Vivado Design Suite. It is a compiled-language simulator that supports mixed-language, Tcl scripts, encrypted IP and enhanced verification.

The Vivado IP Integrator allows engineers to quickly integrate and configure IP from the large Xilinx IP library. The Integrator is also tuned for MathWorks Simulink designs built with Xilinx's System Generator and Vivado High-Level Synthesis.[20]

The Vivado Tcl Store is a scripting system for developing add-ons to Vivado, and can be used to add and modify Vivado's capabilities.[19] Tcl is the scripting language on which Vivado itself is based.[19] All of Vivado's underlying functions can be invoked and controlled via Tcl scripts.[19]

Device support

Vivado supports Xilinx's 7-series and all the newer devices (UltraScale and UltraScale+ series).[3] For development targeting older Xilinx's devices and CPLDs, the already discontinued Xilinx ISE has to be used.

See also

References

- ↑ 1.0 1.1 1.2 "Xilinx Inc, Form 8-K, Current Report, Filing Date Apr 25, 2012". secdatabase.com. http://edgar.secdatabase.com/846/119312512182086/filing-main.htm.

- ↑ Vivado 2022.1 Release, Xilinx

- ↑ 3.0 3.1 Vivado Design Suite User Guide: Release Notes, Installation, and Licensing (UG973) (v2022.1), April 26, 2022, Xilinx

- ↑ "Vivado Design Suite Evaluation and WebPACK". Xilinx. n.d.. https://www.xilinx.com/products/design-tools/vivado/vivado-webpack.html#architecture.

- ↑ Morris, Kevi (2014-11-18). "FPGAs Cool Off the Datacenter, Xilinx Heats Up the Race". Electronic Engineering Journal. http://www.eejournal.com/archives/articles/20141118-datacenter.

- ↑ 6.0 6.1 "Xilinx and its Ecosystem Demonstrate All Programmable and Smarter Vision Solutions at ISE 2015". 2015-02-04. http://www.prnewswire.com/news-releases/xilinx-and-its-ecosystem-demonstrate-all-programmable-and-smarter-vision-solutions-at-ise-2015-300030385.html.

- ↑ "Xilinx Vivado Design Suite Now Available in WebPACK Edition". SAN JOSE: Design & Reuse. 2012-12-19. http://www.design-reuse.com/news/31035/xilinx-vivado-design-suite-webpack-edition.html.

- ↑ Morris, Kevin (2014-02-25). "Xilinx vs. Altera, Calling the Action in the Greatest Semiconductor Rivalry". Electronic Engineering Journal. http://www.eejournal.com/archives/articles/20140225-rivalry/.

- ↑ Vivado Design Suite, Xilinx Website

- ↑ Vivado Design Suite, First version released in 2012, Xilinx Downloads

- ↑ Xilinx, Inc. (November 17, 2021). Vivado Design Suite User Guide: Design Flows Overview (PDF) (Technical report). p. 49. UG892.

The Vivado simulator, integrated into the Vivado IDE, allows you to simulate the design, add and view signals in the waveform viewer, and examine and debug the design as needed.

- ↑ Joselyn, Louise (2013-12-10). "The road to success is long and hard for eda start ups". New Electronics. http://www.newelectronics.co.uk/electronics-technology/the-road-to-success-is-long-and-hard-for-eda-start-ups/58277/.

- ↑ EDN. "The Vivado Design Suite accelerates programmable systems integration and implementation by up to 4X." Jun 15, 2012. Retrieved Jun 25, 2013.

- ↑ Clive Maxfield, EE Times. "WebPACK edition of Xilinx Vivado Design Suite now available." Dec 20, 2012. Retrieved Jun 25, 2013.

- ↑ Xilinx Accelerates Productivity for Zynq-7000 All Programmable SoCs with the Vivado Design Suite 2014.3, SDK, and New UltraFast Embedded Design Methodology Guide, SAN JOSE, Oct. 8, 2014, Design & Reuse

- ↑ 16.0 16.1 16.2 16.3 "Vivado Design Suite 2014.1 Increases Productivity with Automation of UltraFast Design Methodology and OpenCL Hardware Acceleration". Market Watch. 2014-04-16. http://www.marketwatch.com/story/vivado-design-suite-20141-increases-productivity-with-automation-of-ultrafast-design-methodology-and-opencl-hardware-acceleration-2014-04-16.

- ↑ Maxfield, Clive (2013-07-26). "Free High-Level Synthesis Guide for S/W Engineers". EE Times. http://www.eetimes.com/document.asp?doc_id=1319061.

- ↑ Wilson, Richard (2014-05-27). "How to make slow software run quicker". Electronics Weekly. http://www.electronicsweekly.com/news/components/programmable-logic-and-asic/make-slow-software-run-quicker-2014-05/.

- ↑ 19.0 19.1 19.2 19.3 19.4 Morris, Kevin (2014-05-06). "Viva Vivado!, Xilinx Tunes-Up Tools". Electronic Engineering Journal. http://www.eejournal.com/archives/articles/20140506-vivavivado/.

- ↑ Wilson, Richard (2013-09-11). "Xilinx, MathWorks and National Instruments work on high-level FPGA design". Electronics Weekly. http://www.electronicsweekly.com/news/design/embedded-systems/xilinx-mathworks-and-national-instruments-work-on-high-level-fpga-design-2013-09/.

External links