Engineering:PIC microcontrollers

PIC (usually pronounced /pɪk/) is a family of microcontrollers made by Microchip Technology, derived from the PIC1640[1][2] originally developed by General Instrument's Microelectronics Division. The name PIC initially referred to Peripheral Interface Controller,[3] and was subsequently expanded for a short time to include Programmable Intelligent Computer,[4] though the name PIC is no longer used as an acronym for any term. The first parts of the family were available in 1976; by 2013 the company had shipped more than twelve billion individual parts, used in a wide variety of embedded systems.[5]

The PIC was originally designed as a peripheral for the General Instrument CP1600, the first commercially available single-chip 16-bit microprocessor. To limit the number of pins required, the CP1600 had a complex highly-multiplexed bus which was difficult to interface with, so in addition to a variety of special-purpose peripherals, General Instrument made the programmable PIC1640 as an all-purpose peripheral. With its own small RAM, ROM and a simple CPU for controlling the transfers, it could connect the CP1600 bus to virtually any existing 8-bit peripheral. While this offered considerable power, GI's marketing was limited and the CP1600 was not a success. However, GI had also made the PIC1650, a standalone PIC1640 with additional general-purpose I/O in place of the CP1600 interface. When the company spun off their chip division to form Microchip in 1985, sales of the CP1600 were all but dead, but the PIC1650 and successors had formed a major market of their own, and they became one of the new company's primary products.[6]

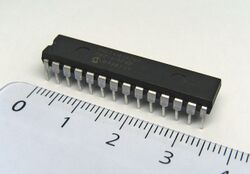

Early models only had mask ROM for code storage, but with its spinoff it was soon upgraded to use EPROM and then EEPROM, which made it possible for end-users to program the devices in their own facilities. All current models use flash memory for program storage, and newer models allow the PIC to reprogram itself. Since then the line has seen significant change; memory is now available in 8-bit, 16-bit, and, in latest models, 32-bit wide. Program instructions vary in bit-count by family of PIC, and may be 12, 14, 16, or 24 bits long. The instruction set also varies by model, with more powerful chips adding instructions for digital signal processing functions. The hardware implementations of PIC devices range from 6-pin SMD, 8-pin DIP chips up to 144-pin SMD chips, with discrete I/O pins, ADC and DAC modules, and communications ports such as UART, I2C, CAN, and even USB. Low-power and high-speed variations exist for many types.

The manufacturer supplies computer software for development known as MPLAB X, assemblers and C/C++ compilers, and programmer/debugger hardware under the MPLAB and PICKit series. Third party and some open-source tools are also available. Some parts have in-circuit programming capability; low-cost development programmers are available as well as high-volume production programmers.

PIC devices are popular with both industrial developers and hobbyists due to their low cost, wide availability, large user base, an extensive collection of application notes, availability of low cost or free development tools, serial programming, and re-programmable flash-memory capability.

History

Original concept

The original PIC was intended to be used with General Instrument's new CP1600 16-bit central processing unit (CPU). In order to fit 16-bit data and address buses into a then-standard 40-pin dual inline package (DIP) chip, the two buses shared the same set of 16 connection pins. In order to communicate with the CPU, devices had to watch other pins on the CPU to determine if the information on the bus was an address or data. Since only one of these was being presented at a time, the devices had to watch the bus to go into address mode, see if that address was part of its memory mapped input/output range, "latch" that address and then wait for the data mode to turn on and then read the value. Additionally, the CP1600 used several external pins to select which device it was attempting to talk to, further complicating the interfacing.

As interfacing devices to the CP1600 could be complex, GI also released the 164x series of support chips with all of the required circuitry built-in. These included keyboard drivers, cassette deck interfaces for storage, and a host of similar systems. For more complex systems, GI introduced the 1640 "Programmable Interface Controller" in 1975. The idea was that a device would use the PIC to handle all the interfacing with the host computer's CP1600, but also use its own internal processor to handle the actual device it was connected to. For instance, a floppy disk drive could be implemented with a PIC talking to the CPU on one side and the floppy disk controller on the other. In keeping with this idea, what would today be known as a microcontroller, the PIC included a small amount of read-only memory (ROM) that would be written with the user's device controller code, and a separate random access memory (RAM) for buffering and working with data. These were connected separately, making the PIC a Harvard architecture system with code and data being stored and managed on separate internal pathways.

In theory, the combination of CP1600 CPU and PIC1640 device controllers provided a very high-performance device control system, one that was similar in power and performance to the channel I/O controllers seen on mainframe computers. In the floppy controller example, for instance, a single PIC could control the drive, provide a reasonable amount of buffering to improve performance, and then transfer data to and from the host computer using direct memory access (DMA) or through relatively simple code in the CPU. The downside to this approach was cost; while the PIC was not necessary for low-speed devices like a keyboard, many tasks would require one or more PICs to build out a complete system.

While the design concept had a number of attractive features, General Instrument never strongly marketed the CP1600, preferring to deal only with large customers and ignoring the low-end market. This resulted in very little uptake of the system, with the Intellivision being the only really widespread use with about three million units. However, GI had introduced a standalone model PIC1650[7] in 1976, designed for use without a CP1600. Although not as powerful as the Intel MCS-48 introduced the same year, it was cheaper, and it found a market.[6] Follow-ons included the PIC1670, with instructions widened from 12 to 13 bits to provide twice the address space (64 bytes of RAM and 1024 words of ROM).[8] When GI spun off its chip division to form Microchip Technology in 1985, production of the CP1600 ended. By this time, however, the PIC1650 had developed a large market of customers using it for a wide variety of roles, and the PIC went on to become one of the new company's primary products.[6]

After the CP1600

In 1985, General Instrument sold their microelectronics division and the new owners cancelled almost everything which by this time was mostly out-of-date. The PIC, however, was upgraded with an internal EPROM to produce a programmable channel I/O controller. At the same time Plessey in the UK released NMOS processors numbered PIC1650 and PIC1655 based on the GI design, using the same instruction sets, either user mask programmable or versions pre-programmed for auto-diallers and keyboard interfaces.[9]

In 1998 Microchip introduced the PIC16F84, a flash programmable and erasable version of its successful serial programmable PIC16C84. In 2001, Microchip introduced more flash programmable devices, with full production commencing in 2002.[10]

Today, a huge variety of PICs are available with various on-board peripherals (serial communication modules, UARTs, motor control kernels, etc.) and program memory from 256 words to 64K words and more. A "word" is one assembly language instruction, varying in length from 8 to 16 bits, depending on the specific PIC microcontroller series.

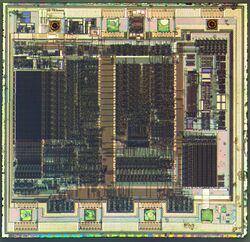

While PIC and PICmicro are now registered trademarks of Microchip Technology, the prefix ″PIC″ is no longer used as an acronym for any term. It is generally thought that PIC stands for "Programmable Intelligent Computer", General Instruments' prefix in 1977 for the PIC1640 and PIC1650 family of microcomputers,[4] replacing the 1976 original meaning "Programmable Interface Controller" for the PIC1640 that was designed specifically to work in combination with the CP1600 microcomputer.[3] The "PIC Series Microcomputers" by General Instrument were a series of Metal-Oxide Semiconductor Large-Scale Integration (MOS/LSI) 8-bit microcomputers containing ROM, RAM, a CPU, and 8-bit input/output (I/O) registers for interfacing. At its time, this technology combined the advantages of MOS circuits with Large-Scale Integration, allowing for the creation of complex integrated circuits with high transistor density.[4]

The Microchip 16C84 (PIC16x84), introduced in 1993, was the first[11] Microchip CPU with on-chip EEPROM memory.

By 2013, Microchip was shipping over one billion PIC microcontrollers every year.Cite error: Closing </ref> missing for <ref> tag

- a memory mapped accumulator

- read access to code memory (table reads)

- direct register-to-register moves (prior cores needed to move registers through the accumulator)

- an external program memory interface to expand the code space

- an 8-bit × 8-bit hardware multiplier

- a second indirect register pair

- auto-increment/auto-decrement addressing controlled by control bits in a status register (ALUSTA)

A significant limitation was that RAM space was limited to 256 bytes (26 bytes of special function registers, and 232 bytes of general-purpose RAM), with awkward bank-switching in the models that supported more.

PIC18

In 2000, Microchip introduced the PIC18 architecture. Unlike the PIC17 series, it has proven to be very popular, with a large number of device variants presently in manufacture. In contrast to earlier devices, which were more often than not programmed in assembly language, C has become the predominant development language.[12]

The PIC18 series inherits most of the features and instructions of the PIC17 series, while adding a number of important new features:

- call stack is 21 bits wide and much deeper (31 levels deep)

- the call stack may be read and written (TOSU:TOSH:TOSL registers)

- conditional branch instructions

- indexed addressing mode (PLUSW)

- the FSR registers are extended to 12 bits, allowing them to linearly address the entire data address space

- the addition of another FSR register (bringing the number up to 3)

The RAM space is 12 bits, addressed using a 4-bit bank select register (BSR) and an 8-bit offset in each instruction. An additional "access" bit in each instruction selects between bank 0 (a=0) and the bank selected by the BSR (a=1).

A 1-level stack is also available for the STATUS, WREG and BSR registers. They are saved on every interrupt, and may be restored on return. If interrupts are disabled, they may also be used on subroutine call/return by setting the s bit (appending ", FAST" to the instruction).

The auto increment/decrement feature was improved by removing the control bits and adding four new indirect registers per FSR. Depending on which indirect file register is being accessed, it is possible to postdecrement, postincrement, or preincrement FSR; or form the effective address by adding W to FSR.

In more advanced PIC18 devices, an "extended mode" is available which makes the addressing even more favorable to compiled code:

- a new offset addressing mode; some addresses which were relative to the access bank are now interpreted relative to the FSR2 register

- the addition of several new instructions, notably for manipulating the FSR registers.

PIC18 devices are still developed (2021) and fitted with CIP (Core Independent Peripherals)

PIC24 and dsPIC

In 2001, Microchip introduced the dsPIC series of chips,[13] which entered mass production in late 2004. They are Microchip's first inherently 16-bit microcontrollers. PIC24 devices are designed as general purpose microcontrollers. dsPIC devices include digital signal processing capabilities in addition.

Although still similar to earlier PIC architectures, there are significant enhancements:[14]

- All registers are 16 bits wide

- Program counter is 22 bits (bits 22:1; bit 0 is always 0)

- Instructions are 24 bits wide

- Data address space expanded to 64 KiB

- First 2 KiB is reserved for peripheral control registers

- Data bank switching is not required unless RAM exceeds 62 KiB

- "f operand" direct addressing extended to 13 bits (8 KiB)

- 16 W registers available for register-register operations.

(But operations on f operands always reference W0.) - Instructions come in byte and (16-bit) word forms

- Stack is in RAM (with W15 as stack pointer); there is no hardware stack

- W14 is the frame pointer

- Data stored in ROM may be accessed directly ("Program Space Visibility")

- Vectored interrupts for different interrupt sources

Some features are:

- (16×16)-bit single-cycle multiplication and other digital signal processing operations

- hardware multiply–accumulate (MAC)

- hardware divide assist (19 cycles for 32/16-bit divide)

- barrel shifting - for both accumulators and general purpose registers

- bit reversal

- hardware support for loop indexing

- peripheral direct memory access

dsPICs can be programmed in C using Microchip's XC16 compiler (formerly called C30), which is a variant of GCC.

Instruction ROM is 24 bits wide. Software can access ROM in 16-bit words, where even words hold the least significant 16 bits of each instruction, and odd words hold the most significant 8 bits. The high half of odd words reads as zero. The program counter is 23 bits wide, but the least significant bit is always 0, so there are 22 modifiable bits.

Instructions come in two main varieties, with most important operations (add, xor, shifts, etc.) allowing both forms:

- The first is like the classic PIC instructions, with an operation between a specified f register (i.e. the first 8K of RAM) and a single accumulator W0, with a destination select bit selecting which is updated with the result. (The W registers are memory-mapped. so the f operand may be any W register.)

- The second form is more conventional, allowing three operands, which may be any of 16 W registers. The destination and one of the sources also support addressing modes, allowing the operand to be in memory pointed to by a W register.

PIC32M MIPS-based line

Microchip's PIC32M products use the PIC trademark, but have a completely different architecture, and are described here only briefly.

PIC32MX

In November 2007, Microchip introduced the PIC32MX family of 32-bit microcontrollers, based on the MIPS32 M4K Core.[15] The device can be programmed using the Microchip MPLAB C Compiler for PIC32 MCUs, a variant of the GCC compiler. The first 18 models currently in production (PIC32MX3xx and PIC32MX4xx) are pin to pin compatible and share the same peripherals set with the PIC24FxxGA0xx family of (16-bit) devices, allowing the use of common libraries, software and hardware tools. Today, starting at 28 pin in small QFN packages up to high performance devices with Ethernet, CAN and USB OTG, full family range of mid-range 32-bit microcontrollers are available.

The PIC32 architecture brought a number of new features to Microchip portfolio, including:

- The highest execution speed 80 MIPS (120+[16] Dhrystone MIPS @ 80 MHz)

- The largest flash memory: 512 kB

- One instruction per clock cycle execution

- The first cached processor

- Allows execution from RAM

- Full Speed Host/Dual Role and OTG USB capabilities

- Full JTAG and 2-wire programming and debugging

- Real-time trace

PIC32MZ

In November 2013, Microchip introduced the PIC32MZ series of microcontrollers, based on the MIPS M14K core. The PIC32MZ series include:[17][18]

- 252 MHz core speed, 415 DMIPS

- Up to 2 MB Flash and 512 KB RAM

- New peripherals including high-speed USB, crypto engine and SQI

In 2015, Microchip released the PIC32MZ EF family, using the updated MIPS M5150 Warrior M-class processor.[19][20]

In 2017, Microchip introduced the PIC32MZ DA Family, featuring an integrated graphics controller, graphics processor and 32MB of DDR2 DRAM.[21][22]

PIC32MM

In June 2016, Microchip introduced the PIC32MM family, specialized for low-power and low-cost applications.[23] The PIC32MM features core-independent peripherals, sleep modes down to 500 nA, and 4 x 4 mm packages.[24] The PIC32MM microcontrollers use the MIPS Technologies M4K, a 32-bit MIPS32 processor. They are meant for very low power consumption and limited to 25 MHz. Their key advantage is to support the 16-bit instructions of MIPS, making program size much more compact (about 40%)

PIC32MK

Microchip introduced the PIC32MK family in 2017, specialized for motor control, industrial control, Industrial Internet of Things (IIoT) and multi-channel CAN applications.[25]

PIC32C Arm-based line

Microchip's PIC32C products also use the PIC trademark, but similarly have a completely different architecture. PIC32C products employ the Arm processor architecture, including various lines using Cortex-M0+, M4, M7, M23, and M33 cores. They are offered in addition to the Arm-based SAM series of MCUs which Microchip inherited from its acquisition of Atmel.[26]

PIC64

Microchip's PIC64 products use the PIC trademark, but have a completely different architecture, and are described here only briefly.

In July 2024, Microchip introduced the PIC64 series of high-performance multi-core microprocessors. The series will initially use the RISC-V instruction set, however Microchip is also planning versions with ARM Cortex-A cores.[27] The PIC64 series will include the PIC64GX line, which focuses on intelligent edge applications, and the PIC64-HPSC line, which is radiation-hardened and focuses on spaceflight applications.[28][29]

Core architecture

The PIC architecture (excluding the unrelated PIC32 and PIC64) is a one-operand accumulator machine like the PDP-8 or the Apollo Guidance Computer. Its characteristics are:

- One accumulator (W0), which is an implied operand of almost every instruction.

- A small number of fixed-length instructions, with mostly fixed timing (2 clock cycles, or 4 clock cycles in 8-bit models).

- A small amount of addressable data space (32, 128, or 256 bytes, depending on the family), extended through banking

- Separate code and data spaces (Harvard architecture).

- Instruction memory is wider than data memory, allowing immediate constants within an instruction. (This is a major difference from the other early accumulator machines mentioned above.)

- The second operand is a memory location or an immediate constant.

- There are no other addressing modes, although an indirect address mode can be emulated using the indirect register(s).

- Data-space mapped CPU, port, and peripheral registers

- ALU status flags are mapped into the data space

- The program counter is also mapped into the data space and writeable (this is used to implement indirect jumps).

- A hardware stack for storing return addresses

- There are only unconditional branch instructions

- Conditional execution is achieved via conditional skip instructions, which conditionally nullify the following instruction.

There is no distinction between memory space and register space because the RAM serves the job of both memory and registers, and the RAM is usually just referred to as "the register file" or simply as "the registers".

Data space (RAM)

PICs have a set of registers that function as general-purpose RAM. Special-purpose control registers for on-chip hardware resources are also mapped into the data space. The addressability of memory varies depending on device series, and all PIC device types have some banking mechanism to extend addressing to additional memory (but some device models have only one bank implemented). Later series of devices feature move instructions, which can cover the whole addressable space, independent of the selected bank. In earlier devices, any register move must be achieved through the accumulator.

To implement indirect addressing, a "file select register" (FSR) and "indirect register" (INDF) are used. A register number is written to the FSR, after which reads from or writes to INDF will actually be from or to the register pointed to by FSR. Later devices extended this concept with post- and pre- increment/decrement for greater efficiency in accessing sequentially stored data. This also allows FSR to be treated almost like a stack pointer (SP).

External data memory is not directly addressable except in some PIC18 devices with high pin count. However, general I/O ports can be used to implement a parallel bus or a serial interface for accessing external memory and other peripherals (using subroutines), with the caveat that such programmed memory access is (of course) much slower than access to the native memory of the PIC MCU.

Code space

The code space is generally implemented as on-chip ROM, EPROM or flash ROM. In general, there is no provision for storing code in external memory due to the lack of an external memory interface. The exceptions are PIC17 and select high pin count PIC18 devices.[30]

Word size

All PICs handle (and address) data in 8-bit chunks. However, the unit of addressability of the code space is not generally the same as the data space. For example, PICs in the baseline (PIC12) and mid-range (PIC16) families have program memory addressable in the same wordsize as the instruction width, i.e. 12 or 14 bits respectively. In contrast, in the PIC18 series, the program memory is addressed in 8-bit increments (bytes), which differs from the instruction width of 16 bits.

In order to be clear, the program memory capacity is usually stated in number of (single-word) instructions, rather than in bytes.

Stacks

PICs have a hardware call stack, which is used to save return addresses. The hardware stack is not software-accessible on earlier devices, but this changed with the PIC18 series devices.

Hardware support for a general-purpose parameter stack was lacking in early series, but this greatly improved in the PIC18 series, making the PIC18 series architecture more friendly to high-level language compilers.

Instruction set

PIC instruction sets vary from about 35 instructions for the low-end PICs to over 80 instructions for the high-end PICs. The instruction set includes instructions to perform a variety of operations on registers directly, on the accumulator and a literal constant, or on the accumulator and a register, as well as for conditional execution, and program branching.

A few operations, such as bit setting and testing, can be performed on any numbered register, but 2-input arithmetic operations always involve W (the accumulator), writing the result back to either W or the other operand register. To load a constant, it is necessary to load it into W before it can be moved into another register. On the older cores, all register moves needed to pass through W, but this changed on the "high-end" cores.

PIC cores have skip instructions, which are used for conditional execution and branching. The skip instructions are "skip if bit set" and "skip if bit not set". Because cores before PIC18 had only unconditional branch instructions, conditional jumps are implemented by a conditional skip (with the opposite condition) followed by an unconditional branch. Skips are also of utility for conditional execution of any immediate single following instruction. It is possible to skip skip instructions. For example, the instruction sequence "skip if A; skip if B; C" will execute C if A is true or if B is false.

The PIC18 series implemented shadow registers: these are registers which save several important registers during an interrupt, providing hardware support for automatically saving processor state when servicing interrupts.

In general, PIC instructions fall into five classes:

- Operation on working register (WREG) with 8-bit immediate ("literal") operand. E.g.

movlw(move literal to WREG),andlw(AND literal with WREG). One instruction peculiar to the PIC isretlw, load immediate into WREG and return, which is used with computed branches to produce lookup tables. - Operation with WREG and indexed register. The result can be written to either the working register (e.g.

addwf reg,w). or the selected register (e.g.addwf reg,f). - Bit operations. These take a register number and a bit number, and perform one of 4 actions: set or clear a bit, and test and skip on set/clear. The latter are used to perform conditional branches. The usual ALU status flags are available in a numbered register so operations such as "branch on carry clear" are possible.

- Control transfers. Other than the skip instructions previously mentioned, there are only two:

gotoandcall. - A few miscellaneous zero-operand instructions, such as return from subroutine, and

sleepto enter low-power mode.

Performance

The architectural decisions are directed at the maximization of speed-to-cost ratio. The PIC architecture was among the first scalar CPU designs and is still among the simplest and cheapest. The Harvard architecture, in which instructions and data come from separate sources, simplifies timing and microcircuit design greatly, and this benefits clock speed, price, and power consumption.

The PIC instruction set is suited to implementation of fast lookup tables in the program space. Such lookups take one instruction and two instruction cycles. Many functions can be modeled in this way. Optimization is facilitated by the relatively large program space of the PIC (e.g. 4096 × 14-bit words on the 16F690) and by the design of the instruction set, which allows embedded constants. For example, a branch instruction's target may be indexed by W, and execute a "RETLW", which does as it is named – return with literal in W.

Interrupt latency is constant at three instruction cycles. External interrupts have to be synchronized with the four-clock instruction cycle, otherwise there can be a one instruction cycle jitter. Internal interrupts are already synchronized. The constant interrupt latency allows PICs to achieve interrupt-driven low-jitter timing sequences. An example of this is a video sync pulse generator. This is no longer true in the newest PIC models, because they have a synchronous interrupt latency of three or four cycles.

Advantages

- Small instruction set to learn

- RISC architecture

- Built-in oscillator with selectable speeds

- Easy entry level, in-circuit programming plus in-circuit debugging PICkit units available for less than $50

- Inexpensive microcontrollers

- Wide range of interfaces including I²C, SPI, USB, UART, A/D, programmable comparators, PWM, LIN, CAN, PSP, and Ethernet[31]

- Availability of processors in DIL package makes them easy to handle for hobby use.

Limitations

- One accumulator

- Register-bank switching is required to access the entire RAM of many devices

- Operations and registers are not orthogonal; some instructions can address RAM and/or immediate constants, while others can use the accumulator only.

The following stack limitations have been addressed in the PIC18 series, but still apply to earlier cores:

- The hardware call stack is not addressable, so preemptive task switching cannot be implemented

- Software-implemented stacks are not efficient, so it is difficult to generate reentrant code and support local variables

With paged program memory, there are two page sizes to worry about: one for CALL and GOTO and another for computed GOTO (typically used for table lookups). For example, on PIC16, CALL and GOTO have 11 bits of addressing, so the page size is 2048 instruction words. For computed GOTOs, where you add to PCL, the page size is 256 instruction words. In both cases, the upper address bits are provided by the PCLATH register. This register must be changed every time control transfers between pages. PCLATH must also be preserved by any interrupt handler.[32]

Compiler development

While several commercial compilers are available, in 2008, Microchip released their own C compilers, C18 and C30, for the line of 18F 24F and 30/33F processors.

As of 2013, Microchip offers their XC series of compilers, for use with MPLAB X. Microchip will eventually phase out its older compilers, such as C18, and recommends using their XC series compilers for new designs.[33]

The RISC instruction set of the PIC assembly language code can make the overall flow difficult to comprehend. Judicious use of simple macros can increase the readability of PIC assembly language. For example, the original Parallax PIC assembler ("SPASM") has macros, which hide W and make the PIC look like a two-address machine. It has macro instructions like mov b, a (move the data from address a to address b) and add b, a (add data from address a to data in address b). It also hides the skip instructions by providing three-operand branch macro instructions, such as cjne a, b, dest (compare a with b and jump to dest if they are not equal).

Hardware features

PIC devices generally feature:

- Flash memory (program memory, programmed using MPLAB devices)

- SRAM (data memory)

- EEPROM (programmable at run-time)

- Sleep mode (power savings)

- Watchdog timer

- Various crystal or RC oscillator configurations, or an external clock

Variants

Within a series, there are still many device variants depending on what hardware resources the chip features:

- General purpose I/O pins

- Internal clock oscillators

- 8/16/32 bit timers

- Synchronous/Asynchronous Serial Interface USART

- MSSP Peripheral for I²C and SPI communications

- Capture/Compare and PWM modules

- Analog-to-digital converters (up to ~1.0 Msps)

- USB, Ethernet, CAN interfacing support

- External memory interface

- Integrated analog RF front ends (PIC16F639, and rfPIC).

- KEELOQ Rolling code encryption peripheral (encode/decode)

- And many more

Trends

The first generation of PICs with EPROM storage have been almost completely replaced by chips with flash memory. Likewise, the original 12-bit instruction set of the PIC1650 and its direct descendants has been superseded by 14-bit and 16-bit instruction sets. Microchip still sells OTP (one-time-programmable) and windowed (UV-erasable) versions of some of its EPROM based PICs for legacy support or volume orders. The Microchip website lists PICs that are not electrically erasable as OTP. UV erasable windowed versions of these chips can be ordered.

Part number

The F in a PICMicro part number generally indicates the PICmicro uses flash memory and can be erased electronically. Conversely, a C generally means it can only be erased by exposing the die to ultraviolet light (which is only possible if a windowed package style is used). An exception to this rule is the PIC16C84, which uses EEPROM and is therefore electrically erasable.

An L in the name indicates the part will run at a lower voltage, often with frequency limits imposed.[34] Parts designed specifically for low voltage operation, within a strict range of 3 – 3.6 volts, are marked with a J in the part number. These parts are also uniquely I/O tolerant as they will accept up to 5 V as inputs.[34]

Development tools

Microchip provides a freeware IDE package called MPLAB X, which includes an assembler, linker, software simulator, and debugger. They also sell C compilers for the PIC10, PIC12, PIC16, PIC18, PIC24, PIC32 and dsPIC, which integrate cleanly with MPLAB X. Free versions of the C compilers are also available with all features. But for the free versions, optimizations will be disabled after 60 days.[35]

Several third parties develop C language compilers for PICs, many of which integrate to MPLAB and/or feature their own IDE. A fully featured compiler for the PICBASIC language to program PIC microcontrollers is available from meLabs, Inc. Mikroelektronika offers PIC compilers in C, BASIC and Pascal programming languages.

A graphical programming language, Flowcode, exists capable of programming 8- and 16-bit PIC devices and generating PIC-compatible C code. It exists in numerous versions from a free demonstration to a more complete professional edition.

The Proteus Design Suite is able to simulate many of the popular 8 and 16-bit PIC devices along with other circuitry that is connected to the PIC on the schematic. The program to be simulated can be developed within Proteus itself, MPLAB or any other development tool.[36]

The standalone FORTH system FlashForth incorporating an interpreter, compiler, assembler and multitasker, provides a comprehensive solution for writing and debugging complex real-time applications. The system, in its entirety, including the compiler, is executing on the microcontroller. A computer with a terminal emulator is used for communicating with FF via a serial or USB link.[37]

Device programmers

Devices called "programmers" are traditionally used to get program code into the target PIC. Most PICs that Microchip currently sells feature ICSP (in-circuit serial programming) and/or LVP (low-voltage programming) capabilities, allowing the PIC to be programmed while it is sitting in the target circuit.

Microchip offers programmers/debuggers under the MPLAB and PICKit series. MPLAB ICD5 and MPLAB REAL ICE are the current programmers and debuggers for professional engineering, while PICKit 5 is a low-cost programmer / debugger line for hobbyists and students. As of 2026, Microchip also produces a pair of further cost-reduced bare-bones programmers/debuggers (with limited capabilities), under the names PICKit Basic and MPLAB Snap.

Bootloading

Many of the higher end flash based PICs can also self-program (write to their own program memory), a process known as bootloading. Demo boards are available with a small factory-programmed bootloader that can be used to load user programs over an interface such as RS-232 or USB, thus obviating the need for a programmer device.

Alternatively there is bootloader firmware available that the user can load onto the PIC using ICSP. After programming the bootloader onto the PIC, the user can then reprogram the device using RS232 or USB, in conjunction with specialized computer software.

The advantages of a bootloader over ICSP is faster programming speeds, immediate program execution following programming, and the ability to both debug and program using the same cable.

Third party

There are many programmers for PIC microcontrollers, ranging from the extremely simple designs which rely on ICSP to allow direct download of code from a host computer, to intelligent programmers that can verify the device at several supply voltages. Many of these complex programmers use a pre-programmed PIC themselves to send the programming commands to the PIC that is to be programmed. The intelligent type of programmer is needed to program earlier PIC models (mostly EPROM type) which do not support in-circuit programming.

Third party programmers range from plans to build your own, to self-assembly kits and fully tested ready-to-go units. Some are simple designs which require a PC to do the low-level programming signalling (these typically connect to the serial or parallel port and consist of a few simple components), while others have the programming logic built into them (these typically use a serial or USB connection, are usually faster, and are often built using PICs themselves for control).

Debugging

In-circuit debugging

All newer PIC devices feature an ICD (in-circuit debugging) interface, built into the CPU core, that allows for interactive debugging of the program in conjunction with MPLAB IDE. MPLAB ICD and MPLAB REAL ICE debuggers can communicate with this interface using the ICSP interface.

This debugging system comes at a price however, namely limited breakpoint count (1 on older devices, 3 on newer devices), loss of some I/O (with the exception of some surface mount 44-pin PICs which have dedicated lines for debugging) and loss of some on-chip features.

Some devices do not have on-chip debug support, due to cost or lack of pins. Some larger chips also have no debug module. To debug these devices, a special -ICD version of the chip mounted on a daughter board which provides dedicated ports is required. Some of these debug chips are able to operate as more than one type of chip by the use of selectable jumpers on the daughter board. This allows broadly identical architectures that do not feature all the on-chip peripheral devices to be replaced by a single -ICD chip. For example: the 16F690-ICD will function as one of six different parts, each of which features none, some or all of five on-chip peripherals.[38]

In-circuit emulators

Microchip offers three full in-circuit emulators: the MPLAB ICE2000 (parallel interface, a USB converter is available); the newer MPLAB ICE4000 (USB 2.0 connection); and most recently, the REAL ICE (USB 2.0 connection). All such tools are typically used in conjunction with MPLAB IDE for source-level interactive debugging of code running on the target.

Operating systems

PIC projects may utilize real-time operating systems such as FreeRTOS, AVIX RTOS, uRTOS, Salvo RTOS or other similar libraries for task scheduling and prioritization.

An open source project by Serge Vakulenko adapts 2.11BSD to the PIC32 architecture, under the name RetroBSD. This brings a familiar Unix-like operating system, including an onboard development environment, to the microcontroller, within the constraints of the onboard hardware.[39]

Clones

Parallax

Parallax produced a series of PICmicro-like microcontrollers known as the Parallax SX. It is currently discontinued. Designed to be architecturally similar to the PIC microcontrollers used in the original versions of the BASIC Stamp, SX microcontrollers replaced the PIC in several subsequent versions of that product.

Parallax's SX are 8-bit RISC microcontrollers, using a 12-bit instruction word, which run fast at 75 MHz (75 MIPS). They include up to 4096 12-bit words of flash memory and up to 262 bytes of random access memory, an eight bit counter and other support logic. There are software library modules to emulate I²C and SPI interfaces, UARTs, frequency generators, measurement counters and PWM and sigma-delta A/D converters. Other interfaces are relatively easy to write, and existing modules can be modified to get new features.

PKK Milandr

Russian PKK Milandr produces microcontrollers using the PIC17 architecture as the 1886 series.[40] [41] [42] [43] Program memory consists of up to 64kB Flash memory in the 1886VE2U (Russian: 1886ВЕ2У) or 8kB EEPROM in the 1886VE5U (1886ВЕ5У). The 1886VE5U (1886ВЕ5У) through 1886VE7U (1886ВЕ7У) are specified for the military temperature range of -60 °C to +125 °C. Hardware interfaces in the various parts include USB, CAN, I2C, SPI, as well as A/D and D/A converters. The 1886VE3U (1886ВЕ3У) contains a hardware accelerator for cryptographic functions according to GOST 28147-89. There are even radiation-hardened chips with the designations 1886VE8U (1886ВЕ8У) and 1886VE10U (1886ВЕ10У).[44]

ELAN Microelectronics

ELAN Microelectronics Corp. in Taiwan make a line of microcontrollers based on the PIC16 architecture, with 13-bit instructions and a smaller (6-bit) RAM address space.[45]

Holtek Semiconductor

Holtek Semiconductor make a large number of very cheap microcontrollers[46] (as low as 8.5 cents in quantity[47]) with a 14-bit instruction set strikingly similar to the PIC16.

Hycon

Hycon Technology, a Taiwanese manufacturer of mixed-signal chips for portable electronics (multimeters, kitchen scales, etc.), has a proprietary H08 microcontroller series with a 16-bit instruction word very similar to the PIC18 family. (No relation to the Hitachi/Renesas H8 microcontrollers.) The H08A[48] is most like the PIC18; the H08B[49] is a subset.[50]

Although the available instructions are almost identical, their encoding is different, as is the memory map and peripherals. For example, the PIC18 allows direct access to RAM at 0x000–0x07F or special function registers at 0xF80–0xFFF by sign-extending an 8-bit address. The H08 places special function registers at 0x000–0x07F and global RAM at 0x080–0x0FF, zero-extending the address.

Other manufacturers in Asia

Many ultra-low-cost OTP microcontrollers from Asian manufacturers, found in low-cost consumer electronics are based on the PIC architecture or modified form. Most clones only target the baseline parts (PIC16C5x/PIC12C50x). With any patents on the basic architecture long since expired, Microchip has attempted to sue some manufacturers on copyright grounds,[51][52] without success.[53][54]

See also

- PIC16x84

- Atmel AVR

- Arduino

- BASIC Atom

- BASIC Stamp

- OOPic

- PICAXE

- TI MSP430

- Maximite

References

- ↑ PIC1650A 8 Bit Microcomputer (PDF) (Datasheet). General Instrument Corp. Archived from the original (PDF) on 2012-03-23. Retrieved 2011-06-29.

- ↑ "PIC16F seminar presentation: History of the Baseline family of Products". p. 4. http://www.microchip.com.tw/PDF/2004_spring/PIC16F%20seminar%20presentation.pdf#page=4.

- ↑ 3.0 3.1 "MOS DATA 1976", General Instrument 1976 Databook

- ↑ 4.0 4.1 4.2 "1977 Data Catalog: Microelectronics". General Instrument Corporation. http://www.rhoent.com/pic16xx.pdf.

- ↑ Cite error: Invalid

<ref>tag; no text was provided for refs named12bil - ↑ 6.0 6.1 6.2 Leibson, Steven (2 January 2023). "A History of Early Microcontrollers, Part 9: The General Instruments PIC1650". Electronic Engineering Journal. https://www.eejournal.com/article/a-history-of-early-microcontrollers-part-9-the-general-instruments-pic1650/.

- ↑ Gruppuso, Frank M. (1982). "Chapter 35 PIC1650: Chip Architecture and Operation". Computer Structures: Principles and Examples. McGraw-Hill. ISBN 0-07-057302-6. https://gordonbell.azurewebsites.net/tcmwebpage/computertimeline/chap35_pic1650_cs2.pdf. Retrieved 2024-08-18.

- ↑ General Instrument. PIC1670 8-bit Microcomputer (PDF) (Data Sheet). Retrieved 2024-08-18.

- ↑ Plessey Satellite Cable TV Integrated Circuit Handbook May 1986

- ↑ Dunn, D. (31 August 2001). "Microchip offering flash at OTP prices". EETimes. https://www.eetimes.com/microchip-offering-flash-at-otp-prices/.

- ↑ "Chip Hall of Fame: Microchip Technology PIC 16C84 Microcontroller". IEEE Spectrum. 30 June 2017. https://spectrum.ieee.org/chip-hall-of-fame-microchip-technology-pic-16c84-microcontroller. Retrieved September 16, 2018.

- ↑ "Microchip PIC micros and C - source and sample code". https://www.microchipc.com/sourcecode/.

- ↑ "MICROCHIP TECHNOLOGY DEBUTS WORLD'S HIGHEST PERFORMING 16-BIT MICROCONTROLLERS". Microchip. 2001-10-01. http://www.microchip.com/stellent/idcplg?IdcService=SS_GET_PAGE&nodeId=2018&mcparam=en013529.

- ↑ "PIC24H Family Overview". https://ww1.microchip.com/downloads/en/DeviceDoc/70166A.pdf.

- ↑ "MIPS32® M4K® Core - MIPS Technologies -MIPS Everywhere - MIPS Technologies". http://www.mips.com/products/processors/32-64-bit-cores/mips32-m4k/.

- ↑ "32-bit PIC MCUs". http://www.microchip.com/en_US/family/pic32/.

- ↑ "32-Bit MCUs - Microchip Technology". https://www.microchip.com/design-centers/32-bit.

- ↑ "Microchip's PIC32MZ 32-bit MCUs Have Class-Leading Performance of 330 DMIPS and 3.28 CoreMarks™/MHz; 30% Better Code Density". Microchip. 2013-11-18. http://www.microchip.com/pagehandler/en-us/press-release/microchips-pic32mz-32-bit-mcus.html.

- ↑ "Welcome to the Imagination Blog". 16 September 2015. http://blog.imgtec.com/mips-processors/microchip-upgrades-pic32mz-ef-family-to-mips-m-class-m5150-mcu.

- ↑ "PIC32MZ EF | Microchip Technology". http://www.microchip.com/design-centers/32-bit/architecture/pic32mz-family.

- ↑ "Microchip Introduces the Industry's First MCU with Integrated 2D GPU and Integrated DDR2 Memory for Groundbreaking Graphics Capabilities". https://www.microchip.com/pressreleasepage/microchip-introduces-PIC32MZDA.

- ↑ "PIC32MZ DA Family". Microchip. http://www.microchip.com/design-centers/32-bit/architecture/pic32mz-da-family.

- ↑ "Microchip Launches Lowest Power, Cost-Effective PIC32 Family - Microchip Technology". https://www.microchip.com/en/pressreleasepage/microchip-launches-lowest-power-cost-effective-pic32-family.

- ↑ "PIC32MM Family of eXtreme Low Power (XLP), Low Cost, 32-bit Microcontrollers". https://www.microchip.com/en-us/products/microcontrollers-and-microprocessors/32-bit-mcus/pic32-32-bit-mcus/pic32mm.

- ↑ "PIC32MK Family". Microchip. http://www.microchip.com/design-centers/32-bit/architecture/pic32mk-family.

- ↑ "32-bit PIC® and SAM Microcontrollers". Microchip. https://www.microchip.com/en-us/products/microcontrollers-and-microprocessors/32-bit-mcus.

- ↑ anisha (12 July 2024). "Microchip starts 64bit PIC64 family with RISC-V" (Press release). RISC-V International. Retrieved 2024-07-24.

- ↑ Lewis, James (9 July 2024). "Microchip Unveils 64-Bit Multi-Core PIC64 Portfolio" (Press release). Microchip. Retrieved 2024-07-24 – via Hackster.io.

- ↑ "Moog Unveils New, Radiation-Hardened Space Computer to Support the Next Generation of High-Speed Computing On-Orbit" (Press release). Moog Inc. 13 August 2024 – via SpaceNews.

- ↑ Rovnak, Tim (2003). "AN869: External Memory Interfacing Techniques for the PIC18F8XXX". Microchip Technology. https://ww1.microchip.com/downloads/en/AppNotes/00869b.pdf.

- ↑ "Microchip Advanced Part Selector". Microchip. http://www.microchip.com/maps/Microcontroller.aspx.

- ↑ "Slowing 208.80.153.50,10-192-48-43&c=1&t=43197.5553483796". http://massmind.org/techref/microchip/pages.htm.

- ↑ "MPLAB® XC: Compiler Solutions". http://www.microchip.com/pagehandler/en_us/devtools/mplabxc/.

- ↑ 34.0 34.1 "3V Design Center". http://www.microchip.com/stellent/idcplg?IdcService=SS_GET_PAGE&nodeId=2530.

- ↑ "MPLAB XC8 Compiler for PIC10/12/16/18 MCUs". http://www.microchip.com/stellent/idcplg?IdcService=SS_GET_PAGE&nodeId=1406&dDocName=en010014.

- ↑ "How to Simulate PIC Microcontroller in Proteus Design Suite 8 - Circuits Gallery" (in en-US). 2013-08-02. http://www.circuitsgallery.com/2013/08/proteus-pic-simulation2.html.

- ↑ "FlashForth" (in en). https://flashforth.com.

- ↑ Microchip document No. DS51292R

- ↑ "start - RetroBSD". http://retrobsd.org/wiki/doku.php.

- ↑ "Milandr K1886VE: The PIC That Went to Russia". The CPU Shack. 10 March 2016. http://www.cpushack.com/2016/03/10/milandr-k1886ve-the-pic-that-went-to-russia/.

- ↑ "Высокопроизводительные 8-ми разрядные КМОП микроконтроллеры 1886ВЕ1 и 1886ВЕ2. Перечень отличий от ближайшего функционального аналога PIC17C756A." (in ru). PKK Milandr. 7 September 2006. http://www.milandr.ru/uploads/Products/product_24/spec_1886BE2(BE1)_otlichiya_PIC17C756A.pdf.

- ↑ "Каталог продукции группы компаний "Миландр" 2017" (in ru). PKK Milandr. http://www.milandr.ru/upload/iblock/fa0/fa022494a4d32d329ffc0c93f61b5d47.pdf.

- ↑ "1886ая серия" (in ru). http://www.155la3.ru/k1886.htm.

- ↑ "Part II: How to "open" microchip and what's inside? Z80, Multiclet, MSP430, PIC and more". ZeptoBars. 21 February 2013. https://zeptobars.com/en/read/open-microchip-asic-what-inside-II-msp430-pic-z80.

- ↑ "義隆電子股份有限公司義隆電子,再創未來!". http://www.emc.com.tw/eng/products.asp.

- ↑ Carlson, Jay (15 September 2017). "Holtek HT-66". The Amazing $1 Microcontroller. https://jaycarlson.net/pf/holtek-ht-66/.

- ↑ Aufranc, Jean-Luc (3 August 2016). "What's the Cheapest MCU? My Try: Holtek HT48R002 8-bit MCU Selling for $0.085". CNX Software blog. https://www.cnx-software.com/2016/08/03/whats-the-cheapest-mcu-my-try-holtek-ht48r002-8-bit-mcu-selling-for-0-085/.

- ↑ "Instruction Set H08A User's Manual". Hycon Technology Corp.. 1 August 2010. https://www.hycontek.com/wp-content/uploads/APD-CORE002_EN.pdf. Retrieved 2025-01-04.

- ↑ "Instruction Set H08B User's Manual". Hycon Technology Corp.. 1 August 2010. https://www.hycontek.com/hy_mcu/APD-CORE003_EN.pdf. Retrieved 2016-08-19.

- ↑ "CPU Core Application Description: Comparisons and Supplements of Instruction Set H08A and H08B". Hycon Technology Corp.. 24 March 2011. https://www.hycontek.com/hy_mcu/APD-CORE001_EN.pdf#page=3.

- ↑ "Microchip Technology files copyright infringement suit against MICON Design Technology CO. LTD" (PDF) (Press release). 29 January 1999. Retrieved 23 October 2017.

- ↑ "Microchip Technology takes legal action against Shanghai Haier Integrated Circuit" (PDF) (Press release). 5 July 2007. Retrieved 23 October 2017.

- ↑ Fuller, Brian (1 May 2013). "Fight Chinese Counterfeiting? Forget It". Electronics Business News. https://epsnews.com/2013/05/01/fight-chinese-counterfeiting-forget-it/.

- ↑ "Haier Integrated chip to win the patent battle against US microchip". 18 May 2015. http://sb2a0.weebly.com/blog/haier-integrated-chip-to-win-the-patent-battle-against-us-microchip.

Further reading

- Microcontroller Theory and Applications, with the PIC18F; 2nd Ed; M. Rafiquzzaman; Wiley; 544 pages; 2018; ISBN 978-1119448419.

- Microcontroller System Design Using PIC18F Processors; Nicolas K. Haddad; IGI Global; 428 pages; 2017; ISBN 978-1683180005.

- PIC Microcontroller Projects in C: Basic to Advanced (for PIC18F); 2nd Ed; Dogan Ibrahim; Newnes; 660 pages; 2014; ISBN 978-0080999241. (1st Ed)

- Microcontroller Programming: Microchip PIC; Sanchez and Canton; CRC Press; 824 pages; 2006; ISBN 978-0849371899. (1st Ed)

- PIC Microcontroller Project Book; John Iovine; TAB; 272 pages; 2000; ISBN 978-0071354790. (1st Ed)

External links

| Wikibooks has a book on the topic of: A Guide To PIC Microcontroller Documentation |

| Wikibooks has a book on the topic of: Embedded Systems/PIC Microcontroller |

.

|