Engineering:R3000

| Designer | MIPS Computer Systems |

|---|---|

| Bits | 32-bit |

| Design | RISC |

The R3000 is a 32-bit RISC microprocessor chipset developed by MIPS Computer Systems that implemented the MIPS I instruction set architecture (ISA). Introduced in June 1988, it was the second MIPS implementation, succeeding the R2000 as the flagship MIPS microprocessor. It operated at 20, 25 and 33.33 MHz.

The MIPS 1 instruction set is small compared to those of the contemporary 80x86 and 680x0 architectures, encoding only more commonly used operations and supporting few addressing modes. Combined with its fixed instruction length and only three different types of instruction formats, this simplified instruction decoding and processing. It employed a 5-stage instruction pipeline, enabling execution at a rate approaching one instruction per cycle, unusual for its time.

This MIPS generation supports up to four co-processors. In addition to the CPU core, the R3000 microprocessor includes a Control Processor (CP), which contains a Translation Lookaside Buffer and a Memory Management Unit.[1] The CP works as a coprocessor. Besides the CP, the R3000 can also support an external R3010 numeric coprocessor,[2] along with two other external coprocessors.

The R3000 CPU does not include level 1 cache. Instead, its on-chip cache controller operates external data and instruction caches of up to 256 KB each. It can access both caches during the same clock cycle.

The R3000 found much success and was used by many companies in their workstations and servers. Users included:

- Ardent Computer

- Atari COJAG (A modified Atari Jaguar for arcade systems).

- Digital Equipment Corporation (DEC) for their DECstation workstations and multiprocessor DECsystem servers.

- Evans & Sutherland for their Vision (ESV) series workstations.

- LSI Logic for their CW4003 RISC processor core and DCAM-101 system-on-a-chip.[3]

- MIPS Computer Systems for their MIPS RISC/os Unix workstations and servers.

- NEC for their RISC EWS4800 workstations and UP4800 servers.

- Prime Computer

- Pyramid Technology

- Seiko Epson

- Silicon Graphics for their Professional IRIS, Personal IRIS and Indigo workstations, and the multiprocessor Power Series visualization systems.

- Sony for their PlayStation and PlayStation 2 (SCPH-10000 to SCPH-700XX - clocked at 37.5 MHz for use as an I/O CPU and at 33.8 MHz for compatibility with PlayStation games) video game consoles, and NEWS workstations, as well as the Bemani System 573 Analog arcade unit, which runs on the R3000A.

- Tandem Computers for their NonStop Cyclone/R and CLX/R fault-tolerant servers.

- Whitechapel Workstations for their Hitech-20 workstation.

- New Horizons Probe [4][5][6]

The R3000 was also used as an embedded microprocessor. When advances in technology rendered it obsolete for high-performance systems, it found continued use in lower-cost designs. Companies such as LSI Logic developed derivatives of the R3000 specifically for embedded systems.

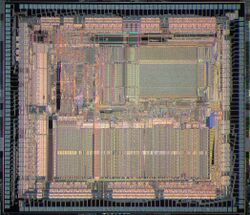

The R3000 was a further development of the R2000 with minor improvements including larger TLB and a faster bus to the external caches. The R3000 die contained 115,000 transistors and measured about 75,000 square mils (48 mm2).[7] MIPS was a fabless semiconductor company, so the R3000 was fabricated by MIPS partners including Integrated Device Technology (IDT), LSI Logic, NEC Corporation, Performance Semiconductor, and others. It was fabricated in a 1.2 μm complementary metal–oxide–semiconductor (CMOS) process[1] with two levels of aluminium interconnect.

Derivatives of the R3000 for non-embedded applications include:

- R3000A - A further development by MIPS introduced in 1989. It operated at clock frequencies up to 40 MHz.

- PR3400 - Developed by Performance Semiconductor, introduced in May 1991, also at up to 40 MHz. It integrated the Performance Semiconductor PR3000A and PR3010A onto a single die.

Derivatives of the R3000 for embedded applications include:

- CW4003, DCAM-101 - Aimed at digital camera applications, the CW4003 core featured a "multiplier-addition bolt-on" (MABO) unit for accelerated integer arithmetic and a pixel-processing accelerator (PPA) unit accessible via the coprocessor 2 interface. The DCAM-101 combined the CW4003 core with modules interfacing to a camera sensor, display, storage and other peripherals, also incorporating a JPEG compression/decompression unit.[3]

- PR31500, PR31700 - Microprocessors from Philips Semiconductors used in the Philips Velo handheld PC range. The 75 MHz PR31700 was fabricated in a 350 nm process, delivered in a 208-pin LQFP, it operated at 3.3 V and dissipated only 350 mW.[citation needed]

- RISController - A family of low-end microcontrollers from IDT. Models include the R3041, R3051, R3052, R3071 and R3081.

- TX3900 - A microcontroller from Toshiba.

- Mongoose-V - A radiation-hardened and expanded 10–15 MHz CPU for use on spacecraft, it is still in use today in applications such as NASA's New Horizons space probe.

References

- ↑ 1.0 1.1 Jurij Šilc; Borut Robič; Theo Ungerer (1999). Processor Architecture: From Dataflow to Superscalar and Beyond. Springer-Verlag Berlin Heidelberg. p. 38. ISBN 978-3-540-64798-0. https://books.google.com/books?id=LYerCAAAQBAJ&pg=PA38.

- ↑ Rowen, Chris; Johnson, Mark; Ries, Paul (June 1988). "The MIPS R3010 Floating-Point Coprocessor". IEEE Micro (The Institute of Electrical and Electronics Engineers) 8 (3): 53–62. doi:10.1109/40.540. ISSN 0272-1732. https://archive.org/details/ieee_micro_v8n3_june_88/page/n54/mode/1up. Retrieved 24 April 2022.

- ↑ 3.0 3.1 Archide, Reynaldo (March 1998). "A Flexible CPU for Digital Cameras". Byte: 49–50. https://archive.org/details/eu_BYTE-1998-03_OCR/page/n76/mode/1up. Retrieved 17 August 2023.

- ↑ Sharma, Aashish (21 July 2015). "The Original PlayStation CPU is Powering New Horizons". http://fossbytes.com/the-original-playstation-cpu-is-powering-new-horizons/.

- ↑ Tomson, Iain (14 January 2015). "PlayStation-processor-powered plutonium probe prepares Pluto pics". https://www.theregister.co.uk/2015/01/14/new_horizons_spacecraft_prepares_to_give_us_our_closest_look_yet_at_pluto/.

- ↑ Dockrill, Peter (17 July 2015). "NASA's New Horizon Probe Made It to Pluto With a PlayStation CPU For a Brain". http://www.sciencealert.com/nasa-s-new-horizon-probe-made-it-to-pluto-with-a-playstation-cpu-for-a-brain.

- ↑ Michael Slater, ed (1992). A Guide to RISC microprocessors. Academic Press, Inc.. p. 129. ISBN 978-0-12-649140-1. https://books.google.com/books?id=shqJUaKB9RMC&pg=PA129.

Further reading

- Rowen, Chris; Johnson, Mark; Ries, Paul (June 1988). "The MIPS R3010 Floating-Point Coprocessor". IEEE Micro 8 (3): 53–62. doi:10.1109/40.540.

|