Engineering:HRS-100

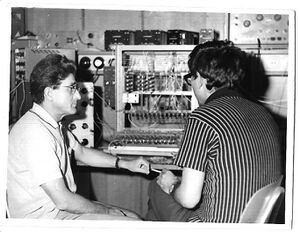

HRS-100 deployed in USSR Academy in Moscow | |

| Developer | Mihajlo Pupin Institute and engineers from USSR |

|---|---|

| Generation | Third generation computer |

| Release date | 1971 |

| Units sold | 3 |

| CPU | 32-bit TTL MSI |

HRS-100, ХРС-100, GVS-100 or ГВС-100, (see Ref.#1, #2, #3 and #4) (Serbo-Croatian: Hibridni Računarski Sistem, Russian: Гибридная Вычислительная Система, English: Hybrid Computer System) was a third generation hybrid computer developed by Mihajlo Pupin Institute (Serbia, then SFR Yugoslavia) and engineers from USSR in the period from 1968 to 1971. Three systems HRS-100 were deployed in Academy of Sciences of USSR in Moscow and Novosibirsk (Akademgorodok) in 1971 and 1978. More production was contemplated for use in Czechoslovakia and German Democratic Republic (DDR), but that was not realised.

HRS-100 was invented and developed to study the dynamical systems in real and accelerated scale time and for efficient solving of wide array of scientific tasks at the institutes of the A.S. of USSR (in the fields: Aerospace-nautics, Energetics, Control engineering, Microelectronics, Telecommunications, Bio-medical investigations, Chemical industry etc.).

Overview

HRS-100 was composed of:

- Digital computer:

- central processor

- 16 kilowords of 0.9 μs 36-bit magnetic core primary memory, expandable to 64 kilowords.

- secondary disk storage

- peripheral devices (teleprinters, punched tape reader/punchers, parallel printers and punched card readers).

- multiple Analog computer modules

- Interconnection devices

- multiple analog and digital Peripheral devices

Central processing unit

HRS-100 has a 32-bit TTL MSI processor with following capabilities:

- four basic arithmetic operations are implemented in hardware for both fixed point and floating point operations

- Addressing modes: immediate/literal, absolute/direct, relative, unlimited-depth multi-level memory indirect and relative-indirect

- 7 index registers and dedicated "index arithmetic" hardware

- 32 interrupt "channels" (10 from within the CPU, 10 from peripherals and 12 from interconnection devices and analog computer)

Primary memory

Primary memory was made up of 0.9 μs cycle time magnetic core modules. Each 36-bit word is organized as follows:

- 32 data bits

- 1 parity bit

- 3 program protection bits specifying which program (Operating System and up to 7 running applications) has access

Secondary storage

Secondary storage was composed of up to 8 of the CDC 9432D removable-media disk drive devices. Capacity of one set of disk platters was about 4 million 6-bit words or 768,000 words of HRS-100 computer. Total, combined, capacity of 8 drives is, therefore, 6,144,000 words. Each disk set comprised 6 platters out of which 10 surfaces are used. Data was organized into 100 cylinders and 16 1536-bit sectors (48 HRS-100 words).

Average data access time was 100 ms (max. 165 ms). Maximum seek time was 25 ms. Raw transfer sector write speed was 208,333 characters/s.

Peripherals

Peripherals communicate with the computer using interrupts and full length of HRS-100 words. Each separate unit has its own controller. Following devices were produced or planned:

- 5 to 8 channel Punched tape reader type PE 1001 (500-1000 characters/s)

- 5 to 8 channel Tape puncher type PE 4060 (150 characters/s)

- IBM 735 teleprinter (88 character set, 7-bit data + 1 parity bit, printing speed: 15 characters/s)

- Fast line printer DP 2440 (up to 700 lines/min, 64-character set, 132 characters per line)

- Standard 80-column punched card reader DP SR300 (reading up to 300 cards/min)

Interconnection hardware

Interconnection hardware (called simply "Link") connects digital and analog components of HRS-100 into a single unified computer. It comprised:

- Control unit for exchange of logic signals

- Blocks of Aanalog-to-digital and digital-to-analog converters

- 16-bit 100 μs clock generator

- Conversion channel relay block

- Power supply

Link takes commands from a digital computer component and organizes their execution via 2 32-bit data channels, 11 control channels, synchronization signals via 3 channels and 9 interrupt channels. Connection between a digital and analog computers is established through a "common-control panel" and two separate consoles. Communicating digital data with analog consoles is done through 16 control, 16 sensitivity, 16 indicator and 10 functional "lines".

Analog-to-digital conversion is achieved by a single signed 14-bit 70,000 samples/s A/D converter and a 32-channel multiplexer. Digital-to-analog conversion is achieved by 16 independent signed 14-bit D/A converters with double registers. Typical D/A conversion took 2 μs.

Analog computer

Analog component of HRS-100 system is composed of up to seven analog machines all connected to the common-control panel. It contains all elements required to independently solve linear and non-linear differential equations, both directly and iteratively.

Units of analog computer:

- linear analog calculation elements

- non-linear analog calculation elements

- parallel logic elements

- electronic potentiometer system

- calculation module and parallel logic control system

- periodic block

- control system

- address system

- measurement system

- exchangeable program board (analog and digital)

- reference voltage supply

Linear analog computer elements were designed to facilitate 0.01% precision in static mode and 0.1% in dynamic mode, for signals up to 1kHz. Non-linear elements precision was not required to be better than 0.1%.

Analog component of HRS-100 has its own peripheral units:

- multi-channel ultraviolet writer

- three-colour oscilloscope

- X-Y writer

Development team

HRS-100 was designed and developed by the following team (see Ref.#1, #4, #5, and #6):

- Principal Science Researchers: Prof. Boris Yakovlevich Kogan (Institute of Control Sciences - IPU AN.USSR, Moscow), Petar Vrbavac and Georgi Konstantinov (Mihajlo Pupin Institute, Belgrade).

- Chief designers:

- Digital part: Svetomir Ojdanić, Dušan Hristović (SFRY), A. Volkov, V. Lisikov (USSR)

- Analogue part: B.J.Kogan, N. N. Mihaylov (USSR), Slavoljub Marjanović, Pavle Pejović (SFRY)

- Link: Milan Hruška, Čedomir Milenković (SFRY), A. G. Spiro (USSR)

- Software: E. A. Trahtengerc, S.J.Vilenkin, V. L. Arlazarov (USSR), Nedeljko Parezanović (SFRY).

See also

- History of computer hardware in the SFRY

- Mihajlo Pupin Institute

- List of Soviet computer systems

Reference literature

- HRS-100 (Hardware and Design Principles), pp. 3–52, by prof. Boris J.Kogan(Ed), IPU AN.USSR, Moscow, 1974 (in Russian).

- HRS-100, Proceedings of Intern. Congress AICA-1973, Prague, pp. 305–324, 27–31.August 1973.

- Analog Computing in the Soviet Union, by D. Abramovitch, IEEE Control Systems Magazine, pp. 52–62, June 2005.

- Hybrid Computing System HRS-100, by P.Vrbavac, S.Ojdanic, D.Hristovic, M.Hruska, S.Marjanovic, Proc. of the 6. Int. Symp. on Electronics and Automation, pp. 347–356, Herceg Novi, Yugoslavia, 21–27.June 1971.

- Development of the Computing Technology in Serbia (Razvoj Racunarstva u Srbiji), by Dušan Hristović, Phlogiston journal, No 18/19, pp. 89–105, Museum of the science and technology (MNT-SANU), Belgrade 2010/2011.

- "50 Years of Computing in Serbia"(50 Godina Racunarstva u Srbiji), by D.B.Vujaklija and N.Markovic(Ed),pp. 37–44, DIS,IMP and PC Press, Belgrade 2011. (In Serbian).

|