Engineering:IMPLY gate

From HandWiki

Short description: Digital logic gate

| IMPLY gate truth table | ||

|---|---|---|

| Input | Output | |

| A | B | A → B |

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

The IMPLY gate is a digital logic gate that implements a logical conditional.[1]

Symbols

IMPLY can be denoted in algebraic expressions with the logic symbol right-facing arrow (→). Logically, it is equivalent to material implication, and the logical expression ¬A v B.

There are two symbols for IMPLY gates: the traditional symbol and the IEEE symbol. For more information see Logic gate symbols.

| Image:IMPLY ANSI.svg | Image:IEC Implies gate.svg | |

| Traditional IMPLY Symbol | IEEE IMPLY Symbol |

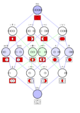

Functional completeness

While the Implication gate is not functionally complete by itself, it is in conjunction with the constant 0 source. This can be shown via the following:

Thus, since the implication gate with the addition of the constant 0 source can create both the NOT gate and the OR gate, it can create the NOR gate, which is a universal gate.

See also

- NIMPLY gate

- AND gate

- NOT gate

- NAND gate

- NOR gate

- XOR gate

- XNOR gate

- Boolean algebra (logic)

- Logic gates

References

-

|