Engineering:POWER6

Power6 CPU | |

| General Info | |

|---|---|

| Launched | 2007 |

| Designed by | IBM |

| Performance | |

| Max. CPU clock rate | 3.6 GHz to 5.0 GHz |

| Cache | |

| L1 cache | 64+64 KB/core |

| L2 cache | 4 MB/core |

| L3 cache | 32 MB/chip (off-chip) |

| Architecture and classification | |

| Min. feature size | 65 nm |

| Instruction set | Power ISA (Power ISA v.2.05) |

| Physical specifications | |

| Cores |

|

| History | |

| Predecessor | POWER5 |

| Successor | POWER7 |

| POWER, PowerPC, and Power ISA architectures |

|---|

| NXP (formerly Freescale and Motorola) |

| IBM |

|

| IBM/Nintendo |

| Other |

| Related links |

| Cancelled in gray, historic in italic |

The POWER6 is a microprocessor developed by IBM that implemented the Power ISA v.2.05. When it became available in systems in 2007, it succeeded the POWER5+ as IBM's flagship Power microprocessor. It is claimed to be part of the eCLipz project, said to have a goal of converging IBM's server hardware where practical (hence "ipz" in the acronym: iSeries, pSeries, and zSeries).[1]

History

POWER6 was described at the International Solid-State Circuits Conference (ISSCC) in February 2006, and additional details were added at the Microprocessor Forum in October 2006[2] and at the next ISSCC in February 2007. It was formally announced on May 21, 2007.[3] It was released on June 8, 2007 at speeds of 3.5, 4.2 and 4.7 GHz,[4] but the company has noted prototypes have reached 6 GHz.[5] POWER6 reached first silicon in the middle of 2005,[6] and was bumped to 5.0 GHz in May 2008 with the introduction of the P595.[7]

Description

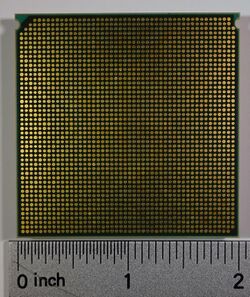

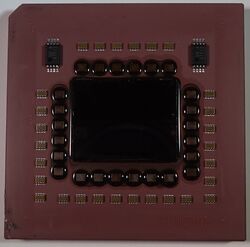

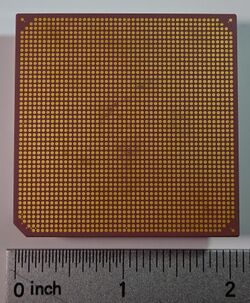

The POWER6 is a dual-core processor. Each core is capable of two-way simultaneous multithreading (SMT). The POWER6 has approximately 790 million transistors and is 341 mm2 large fabricated on a 65 nm process. A notable difference from POWER5 is that the POWER6 executes instructions in-order instead of out-of-order. This change often requires software to be recompiled for optimal performance, but the POWER6 still achieves significant performance improvements over the POWER5+ even with unmodified software, according to the lead engineer on the POWER6 project.[4]

POWER6 also takes advantage of ViVA-2, Virtual Vector Architecture, which enables the combination of several POWER6 nodes to act as a single vector processor.[8]

Each core has two integer units, two binary floating-point units, an AltiVec unit, and a novel decimal floating-point unit. The binary floating-point unit incorporates "many microarchitectures, logic, circuit, latch and integration techniques to achieve [a] 6-cycle, 13-FO4 pipeline", according to a company paper.[9] Unlike the servers from IBM's competitors, the POWER6 has hardware support for IEEE 754 decimal arithmetic and includes the first decimal floating-point unit integrated in silicon. More than 50 new floating point instructions handle the decimal math and conversions between binary and decimal.[10] This feature was also added to the z10 microprocessor featured in the System z10.[8]

Each core has a 64 KB, four-way set-associative instruction cache and a 64 KB data cache of an eight-way set-associative design with a two-stage pipeline supporting two independent 32-bit reads or one 64-bit write per cycle.[9] Each core has semi-private 4 MiB unified L2 cache, where the cache is assigned a specific core, but the other has a fast access to it. The two cores share a 32 MiB L3 cache which is off die, using an 80 GB/s bus.[10]

POWER6 can connect to up to 31 other processors using two inter node links (50 GB/s), and supports up to 10 logical partitions per core (up to a limit of 254 per system). There is an interface to a service processor that monitors and adjusts performance and power according to set parameters.[11]

IBM also makes use of a 5 GHz duty-cycle correction clock distribution network for the processor. In the network, the company implements a copper distribution wire that is 3 μm wide and 1.2 μm thick. The POWER6 design uses dual power supplies, a logic supply in the 0.8-to-1.2 Volt range and an SRAM power supply at about 150-mV higher.[9]

The thermal characteristics of POWER6 are similar to that of the POWER5. Dr Frank Soltis, an IBM chief scientist, said IBM had solved power leakage problems associated with high frequency by using a combination of 90 nm and 65 nm parts in the POWER6 design.[12]

POWER6+

The slightly enhanced POWER6+ was introduced in April 2009, but had been shipping in Power 560 and 570 systems since October 2008. It added more memory keys for secure memory partition, a feature taken from IBM's mainframe processors.[13]

Products

As of 2008[update], the range of POWER6 systems includes "Express" models (the 520, 550 and 560) and Enterprise models (the 570 and 595).[14] The various system models are designed to serve any sized business. For example, the 520 Express is marketed to small businesses while the Power 595 is marketed for large, multi-environment data centers. The main difference between the Express and Enterprise models is that the latter include Capacity Upgrade on Demand (CUoD) capabilities and hot-pluggable processor and memory "books".

| Name | Number of sockets | Number of cores | CPU clock frequency |

|---|---|---|---|

| 520 Express | 2 | 4 | 4.2 GHz or 4.7 GHz |

| 550 Express | 4 | 8 | 4.2 GHz or 5.0 GHz |

| 560 Express | 8 | 16 | 3.6 GHz |

| 570 | 8 | 16 | 4.4 GHz or 5.0 GHz |

| 570 | 16 | 32 | 4.2 GHz |

| 575 | 16 | 32 | 4.7 GHz |

| 595 | 32 | 64 | 4.2 GHz or 5.0 GHz |

IBM also offers four POWER6 based blade servers.[15] Specifications are shown in the table below.

| Name | Number of cores | CPU clock frequency | Blade slots required |

|---|---|---|---|

| BladeCenter JS12 | 2 | 3.8 GHz | 1 |

| BladeCenter JS22 | 4 | 4.0 GHz | 1 |

| BladeCenter JS23 | 4 | 4.2 GHz | 1 |

| BladeCenter JS43 | 8 | 4.2 GHz | 2 |

All blades support AIX, IBM i, and Linux. The BladeCenter S and H chassis is supported for blades running AIX, i, and Linux. The BladeCenter E, HT, and T chassis support blades running AIX and Linux but not i.

At the SuperComputing 2007 (SC07) conference in Reno a new water-cooled Power 575 was revealed. The 575 is composed of 2U "nodes" each with 32 POWER6 cores at 4.7 GHz with up to 256 GB of RAM. Up to 448 cores can be installed in a single frame.

| Name | Number of cores | CPU clock frequency | Number of controllers |

|---|---|---|---|

| DS8700 | 2, 4 | 4.7 GHz | 1, 2 |

| DS8800 | 2, 4, 8 | 5.0 GHz | 1, 2 |

See also

- IBM Power microprocessors

- POWER7

- z10, a mainframe processor sharing much technology with the POWER6.

References

- ↑ "A Mainframe Roadmap". Isham Research. http://www.isham-research.co.uk/mainframe_2008.html.

- ↑ David Kanter (October 16, 2006). "Fall Processor Forum 2006: IBM's POWER6". Real World Technologies. http://www.realworldtech.com/power6-mpf/.

- ↑ "IBM Unleashes World's Fastest Chip in Powerful New Computer" (Press release). IBM. Archived from the original on May 24, 2007.

- ↑ 4.0 4.1 "IBM POWER system hardware". IBM. http://www-03.ibm.com/systems/power/hardware/.

- ↑ Vance, Ashlee (2006-02-07). "IBM thumbs nose at heat concerns, kicks Power6 to 6GHz". The Register. https://www.theregister.co.uk/2006/02/07/ibm_power6_show/.

- ↑ "IBM's Power6 Gets First Silicon as Power5+ Looms". IT Jungle. http://www.itjungle.com/tfh/tfh082205-story01.html.

- ↑ "IBM smacks rivals with 5.0GHz Power6 beast". The Register. https://www.theregister.co.uk/2008/04/08/ibm_595_water/.

- ↑ 8.0 8.1 "An eCLipz Looms on the Horizon". Real World Technologies. http://www.realworldtech.com/page.cfm?ArticleID=RWT121905001634.

- ↑ 9.0 9.1 9.2 "IBM Tips Power6 Processor Architecture". InformationWeek. 6 February 2006. https://www.informationweek.com/it-life/ibm-tips-power6-processor-architecture.

- ↑ 10.0 10.1 "Fall Processor Forum: Power6 at 5 GHz". Heinz Heise. http://www.heise.de/english/newsticker/news/79371.

- ↑ Merritt, Rick (2006-10-10). "IBM cranks dual-core Power6 beyond 4GHz". EE Times. https://www.eetimes.com/ibm-cranks-dual-core-power6-beyond-4ghz/.

- ↑ Roger Howorth (2006-02-08). "IBM's Power6 processor to run at 4GHz in 2007". IT Week. http://www.itweek.co.uk/itweek/news/2150006/ibm-power6-processor-run-4ghz.

- ↑ "IBM Power Systems Announcement Overview". 28 April 2009. http://www-03.ibm.com/systems/resources/systems_power_news_20090428_annc.pdf.

- ↑ "IBM Power Systems Hardware". http://www-03.ibm.com/systems/power/hardware/.

- ↑ "IBM Power Systems Hardware - Blade Servers". http://www-03.ibm.com/systems/power/hardware/blades/index.html.

External links

- IBM POWER6 Press Kit

- "IBM's Power6 gets help with math, multimedia". October 10, 2006. https://www.cnet.com/tech/tech-industry/ibms-power6-gets-help-with-math-multimedia/.

- "IBM Debuts Power6 In New Unix Server". May 21, 2007. https://www.informationweek.com/it-life/ibm-debuts-power6-in-new-unix-server.

- "POWER6 set to carry the POWER4/POWER5/970 lineage forward?". October 19, 2006. https://arstechnica.com/gadgets/2006/10/8034/.

- "IBM unveils POWER6 microprocessor details". February 12, 2007. https://arstechnica.com/uncategorized/2007/02/8823/.

- "IBM's POWER6 flies the coop at 4.7GHz". May 21, 2007. https://arstechnica.com/gadgets/2007/05/ibms-power6-flies-the-coop-at-4-7ghz/.

Recommended reading

- POWER Roadmap, IBM, Oct 2006

- M. J. Mack; W. M. Sauer; S. B. Swaney; B. G. Mealey (November 2007). "IBM POWER6 Reliability". IBM Journal of Research and Development 51 (6): 763–774. doi:10.1147/rd.516.0763.

- R. Berridge; R. M. Averill; A. E. Barish; M. A. Bowen; P. J. Camporese; J. DiLullo; P. E. Dudley; J. Keinert et al. (November 2007). "IBM POWER6 microprocessor physical design and design methodology". IBM Journal of Research and Development 51 (6): 685–714. doi:10.1147/rd.516.0685.

- H. -Y. McCreary; M. A. Broyles; M. S. Floyd; A. J. Geissler; S. P. Hartman; F. L. Rawson; T. J. Rosedahl; J. C. Rubio et al. (November 2007). "EnergyScale for IBM POWER6 microprocessor based systems". IBM Journal of Research and Development 51 (6): 775–786. doi:10.1147/rd.516.0775.

- M. S. Floyd; S. Ghiasi; T. W. Keller; K. Rajamani; F. L. Rawson; J. C. Rubio; M. S. Ware (November 2007). "System power management support in the IBM POWER6 microprocessor". IBM Journal of Research and Development 51 (6): 733–746. doi:10.1147/rd.516.0733.

- H. Q. Le; W. J. Starke; J. S. Fields; F. P. O'Connell; D. Q. Nguyen; B. J. Ronchetti; W. M. Sauer; E. M. Schwarz et al. (November 2007). "IBM POWER6 microarchitecture". IBM Journal of Research and Development 51 (6): 639–662. doi:10.1147/rd.516.0639.

- D. W. Plass; Y. H. Chan (November 2007). "IBM POWER6 SRAM arrays". IBM Journal of Research and Development 51 (6): 747–756. doi:10.1147/rd.516.0747.

- L. Eisen; J. W. Ward; H. -W. Tast; N. Mading; J. Leenstra; S. M. Mueller; C. Jacobi; J. Preiss et al. (November 2007). "IBM POWER6 accelerators: VMX and DFU". IBM Journal of Research and Development 51 (6): 1–21. doi:10.1147/rd.516.0663.

- "POWER: The Sixth Generation". (30 October 2006). Microprocessor Report.

|