Engineering:Pascal (microarchitecture)

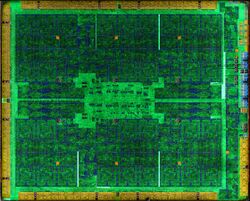

Template:Infobox GPU microarchitecture Pascal is the codename for a GPU microarchitecture developed by Nvidia, as the successor to the Maxwell architecture. The architecture was first introduced in April 2016 with the release of the Tesla P100 (GP100) on April 5, 2016, and is primarily used in the GeForce 10 series, starting with the GeForce GTX 1080 and GTX 1070 (both using the GP104 GPU), which were released on May 17, 2016, and June 10, 2016, respectively. Pascal was manufactured using TSMC's 16 nm FinFET process,[1] and later Samsung's 14 nm FinFET process.[2]

The architecture is named after the 17th century French mathematician and physicist, Blaise Pascal.

In April 2019, Nvidia enabled a software implementation of DirectX Raytracing on Pascal-based cards starting with the GTX 1060 6 GB, and in the 16 series cards, a feature reserved to the Turing-based RTX series up to that point.[3][4]

Details

In March 2014, Nvidia announced that the successor to Maxwell would be the Pascal microarchitecture; announced on May 6, 2016, and released on May 27 of the same year. The Tesla P100 (GP100 chip) has a different version of the Pascal architecture compared to the GTX GPUs (GP104 chip). The shader units in GP104 have a Maxwell-like design.[5]

Architectural improvements of the GP100 architecture include the following:[6][7][8]

- In Pascal, an SM (streaming multiprocessor) consists of between 64-128 CUDA cores, depending on if it is GP100 or GP104. Maxwell packed 128, Kepler 192, Fermi 32 and Tesla only 8 CUDA cores into an SM; the GP100 SM is partitioned into two processing blocks, each having 32 single-precision CUDA Cores, an instruction buffer, a warp scheduler, 2 texture mapping units and 2 dispatch units.

- CUDA Compute Capability 6.0.

- High Bandwidth Memory 2 — some cards feature 16 GiB HBM2 in four stacks with a total of 4096-bit bus with a memory bandwidth of 720 GB/s.

- Unified memory — a memory architecture, where the CPU and GPU can access both main system memory and memory on the graphics card with the help of a technology called "Page Migration Engine".

- NVLink — a high-bandwidth bus between the CPU and GPU, and between multiple GPUs. Allows much higher transfer speeds than those achievable by using PCI Express; estimated to provide between 80 and 200 GB/s.[9][10]

- 16-bit (FP16) floating-point operations (colloquially "half precision") can be executed at twice the rate of 32-bit floating-point operations ("single precision")[11] and 64-bit floating-point operations (colloquially "double precision") executed at half the rate of 32-bit floating point operations.[12]

- More registers — twice the amount of registers per CUDA core compared to Maxwell.

- More shared memory.

- Dynamic load balancing scheduling system.[13] This allows the scheduler to dynamically adjust the amount of the GPU assigned to multiple tasks, ensuring that the GPU remains saturated with work except when there is no more work that can safely be distributed to distribute.[13] Nvidia therefore has safely enabled asynchronous compute in Pascal's driver.[13]

- Instruction-level and thread-level preemption.[14]

Architectural improvements of the GP104 architecture include the following:[5]

- CUDA Compute Capability 6.1.

- GDDR5X — new memory standard supporting 10Gbit/s data rates, updated memory controller.[15]

- Simultaneous Multi-Projection - generating multiple projections of a single geometry stream, as it enters the SMP engine from upstream shader stages.[16]

- DisplayPort 1.4, HDMI 2.0b.

- Fourth generation Delta Color Compression.

- Enhanced SLI Interface — SLI interface with higher bandwidth compared to the previous versions.

- PureVideo Feature Set H hardware video decoding HEVC Main10(10bit), Main12(12bit) and VP9 hardware decoding.

- HDCP 2.2 support for 4K DRM protected content playback and streaming (Maxwell GM200 and GM204 lack HDCP 2.2 support, GM206 supports HDCP 2.2).[17]

- NVENC HEVC Main10 10bit hardware encoding.

- GPU Boost 3.0.

- Instruction-level preemption.[14] In graphics tasks, the driver restricts preemption to the pixel-level, because pixel tasks typically finish quickly and the overhead costs of doing pixel-level preemption are lower than instruction-level preemption (which is expensive).[14] Compute tasks get thread-level or instruction-level preemption,[14] because they can take longer times to finish and there are no guarantees on when a compute task finishes. Therefore the driver enables the expensive instruction-level preemption for these tasks.[14]

Overview

Graphics Processor Cluster

A chip is partitioned into Graphics Processor Clusters (GPCs). For the GP104 chips, a GPC encompasses 5 SMs.

Streaming Multiprocessor "Pascal"

A "Streaming Multiprocessor" corresponds to AMD's Compute Unit. An SM encompasses 128 single-precision ALUs ("CUDA cores") on GP104 chips and 64 single-precision ALUs on GP100 chips.

What AMD calls a CU (compute unit) can be compared to what Nvidia calls an SM (streaming multiprocessor). While all CU versions consist of 64 shader processors (i.e. 4 SIMD Vector Units (each 16-lane wide)= 64), Nvidia (regularly calling shader processors "CUDA cores") experimented with very different numbers:

- On Tesla 1 SM combines 8 single-precision (FP32) shader processors

- On Fermi 1 SM combines 32 single-precision (FP32) shader processors

- On Kepler 1 SM combines 192 single-precision (FP32) shader processors and also 64 double-precision (FP64) units (at least the GK110 GPUs)

- On Maxwell 1 SM combines 128 single-precision (FP32) shader processors

- On Pascal it depends:

- On the GP100 1 SM combines 64 single-precision (FP32) shader processors and also 32 double-precision (FP64) providing a 2:1 ratio of single- to double-precision throughput. The GP100 uses more flexible FP32 cores that are able to process one single-precision or two half-precision numbers in a two-element vector.[18] Nvidia intends to address the calculation of algorithms related to deep learning with those.

- On the GP104 1 SM combines 128 single-precision ALUs, 4 double-precision ALUs providing a 32:1 ratio, and one half-precision ALU that contains a vector of two half-precision floats which can execute the same instruction on both floats providing a 64:1 ratio if the same instruction is used on both elements.

Polymorph-Engine 4.0

The Polymorph Engine version 4.0 is the unit responsible for Tessellation. It corresponds functionally with AMD's Geometric Processor. It has been moved from the shader module to the TPC to allow one Polymorph engine to feed multiple SMs within the TPC.[19]

Chips

- GP100: Nvidia Tesla P100 GPU accelerator is targeted at GPGPU applications such as FP64 double precision compute and deep learning training that uses FP16. It uses HBM2 memory.[20] Quadro GP100 also uses the GP100 GPU.

- GP102: This GPU is used in the TITAN Xp,[21] Titan X[22] and the GeForce GTX 1080 Ti. It is also used in the Quadro P6000[23] & Tesla P40.[24]

- GP104: This GPU is used in the GeForce GTX 1070, GTX 1070 Ti and the GTX 1080. The GTX 1070 has 15/20 and the GTX 1070 Ti has 19/20 of its SMs enabled. Both are connected to GDDR5 memory, while the GTX 1080 is a full chip and is connected to GDDR5X memory. It is also used in the Quadro P5000, Quadro P4000, Quadro P3200 (mobile applications) and Tesla P4.

- GP106: This GPU is used in the GeForce GTX 1060 with GDDR5/GDDR5X[25] memory.[26][27] It is also used in the Quadro P2000.

- GP107: This GPU is used in the GeForce GTX 1050 Ti and GeForce GTX 1050. It is also used in the Quadro P1000, Quadro P600, Quadro P620 & Quadro P400.

- GP108: This GPU is used in the GeForce GT 1010 and GeForce GT 1030.

On the GP104 chip an SM consists of 128 single-precision ALUs ("CUDA cores"), on the GP100 of 64 single-precision ALUs. Due to different organization of the chips, like number of double precision ALUs, the theoretical double precision performance of the GP100 is half of the theoretical one for single precision; the ratio is 1/32 for the GP104 chip.

| GK104 | GK110 | GM204 (GTX 970) | GM204 (GTX 980) | GM200 | GP104 | GP100 | |

|---|---|---|---|---|---|---|---|

| Dedicated texture cache per SM | 48 KiB | N/A | N/A | N/A | N/A | N/A | N/A |

| Texture (graphics or compute) or read-only data (compute only) cache per SM | N/A | 48 KiB[28] | N/A | N/A | N/A | N/A | N/A |

| Programmer-selectable shared memory/L1 partitions per SM | 48 KiB shared memory + 16 KiB L1 cache (default)[29] | 48 KiB shared memory + 16 KiB L1 cache (default)[29] | N/A | N/A | N/A | N/A | N/A |

| 32 KiB shared memory + 32 KiB L1 cache[29] | 32 KiB shared memory + 32 KiB L1 cache[29] | ||||||

| 16 KiB shared memory + 48 KiB L1 cache[29] | 16 KiB shared memory + 48 KiB L1 cache[29] | ||||||

| Unified L1 cache/texture cache per SM | N/A | N/A | 48 KiB[30] | 48 KiB[30] | 48 KiB[30] | 48 KiB[30] | 24 KiB[30] |

| Dedicated shared memory per SM | N/A | N/A | 96 KiB[30] | 96 KiB[30] | 96 KiB[30] | 96 KiB[30] | 64 KiB[30] |

| L2 cache per chip | 512 KiB[30] | 1536 KiB[30] | 1792 KiB[31] | 2048 KiB[31] | 3072 KiB[30] | 2048 KiB[30] | 4096 KiB[30] |

Performance

The theoretical single-precision processing power of a Pascal GPU in GFLOPS is computed as 2 X (operations per FMA instruction per CUDA core per cycle) × number of CUDA cores × core clock speed (in GHz).

The theoretical double-precision processing power of a Pascal GPU is 1/2 of the single precision performance on Nvidia GP100, and 1/32 of Nvidia GP102, GP104, GP106, GP107 & GP108.

The theoretical half-precision processing power of a Pascal GPU is 2× of the single precision performance on GP100[12] and 1/64 on GP104, GP106, GP107 & GP108.[18]

Successor

The Pascal architecture was succeeded in 2017 by Volta in the HPC, cloud computing, and self-driving car markets, and in 2018 by Turing in the consumer and business market.[32]

See also

- List of eponyms of Nvidia GPU microarchitectures

- List of Nvidia graphics processing units

- Nvidia NVDEC

- Nvidia NVENC

References

- ↑ "NVIDIA 7nm Next-Gen-GPUs To Be Built By TSMC". Wccftech. 24 June 2018. https://wccftech.com/nvidia-7nm-next-gen-gpus-tsmc/.

- ↑ "Samsung to Optical-Shrink NVIDIA "Pascal" to 14 nm". https://www.techpowerup.com/224976/samsung-to-optical-shrink-nvidia-pascal-to-14-nm.html.

- ↑ "Accelerating The Real-Time Ray Tracing Ecosystem: DXR For GeForce RTX and GeForce GTX". NVIDIA. https://www.nvidia.com/en-us/geforce/news/geforce-gtx-ray-tracing-coming-soon/.

- ↑ "Ray Tracing Comes to Nvidia GTX GPUs: Here's How to Enable It". 11 April 2019. https://www.tomsguide.com/us/ray-tracing-gtx-gpu-driver,news-29847.html.

- ↑ 5.0 5.1 "NVIDIA GeForce GTX 1080". http://international.download.nvidia.com/geforce-com/international/pdfs/GeForce_GTX_1080_Whitepaper_FINAL.pdf.

- ↑ Gupta, Sumit (2014-03-21). "NVIDIA Updates GPU Roadmap; Announces Pascal". Blogs.nvidia.com. http://blogs.nvidia.com/blog/2014/03/25/gpu-roadmap-pascal/.

- ↑ "Parallel Forall". NVIDIA Developer Zone. Devblogs.nvidia.com. http://devblogs.nvidia.com/parallelforall/.

- ↑ "NVIDIA Tesla P100". https://images.nvidia.com/content/pdf/tesla/whitepaper/pascal-architecture-whitepaper.pdf.

- ↑ "Inside Pascal: NVIDIA's Newest Computing Platform". 2016-04-05. https://devblogs.nvidia.com/parallelforall/inside-pascal/.

- ↑ Denis Foley (2014-03-25). "NVLink, Pascal and Stacked Memory: Feeding the Appetite for Big Data". http://devblogs.nvidia.com/parallelforall/nvlink-pascal-stacked-memory-feeding-appetite-big-data/.

- ↑ "NVIDIA's Next-Gen Pascal GPU Architecture to Provide 10X Speedup for Deep Learning Apps". http://blogs.nvidia.com/blog/2015/03/17/pascal/.

- ↑ 12.0 12.1 Smith, Ryan (2015-04-05). "NVIDIA Announces Tesla P100 Accelerator - Pascal GP100 Power for HPC". AnandTech. http://www.anandtech.com/show/10222/nvidia-announces-tesla-p100-accelerator-pascal-power-for-hpc. "Each of those SMs also contains 32 FP64 CUDA cores - giving us the 1/2 rate for FP64 - and new to the Pascal architecture is the ability to pack 2 FP16 operations inside a single FP32 CUDA core under the right circumstances"

- ↑ 13.0 13.1 13.2 Smith, Ryan (July 20, 2016). "The NVIDIA GeForce GTX 1080 & GTX 1070 Founders Editions Review: Kicking Off the FinFET Generation". AnandTech: p. 9. http://www.anandtech.com/show/10325/the-nvidia-geforce-gtx-1080-and-1070-founders-edition-review/9.

- ↑ 14.0 14.1 14.2 14.3 14.4 Smith, Ryan (July 20, 2016). "The NVIDIA GeForce GTX 1080 & GTX 1070 Founders Editions Review: Kicking Off the FinFET Generation". AnandTech: p. 10. http://www.anandtech.com/show/10325/the-nvidia-geforce-gtx-1080-and-1070-founders-edition-review/10.

- ↑ "GTX 1080 Graphics Card". GeForce. http://www.geforce.com/hardware/10series/geforce-gtx-1080.

- ↑ Carbotte, Kevin (2016-05-17). "Nvidia GeForce GTX 1080 Simultaneous Multi-Projection & Async Compute". http://www.tomshardware.com/reviews/nvidia-geforce-gtx-1080-pascal,4572-3.html.

- ↑ "Nvidia Pascal HDCP 2.2". Nvidia Hardware Page. http://www.geforce.com/hardware/10series/geforce-gtx-1080/.

- ↑ 18.0 18.1 Smith, Ryan (July 20, 2016). "The NVIDIA GeForce GTX 1080 & GTX 1070 Founders Editions Review: Kicking Off the FinFET Generation". AnandTech: p. 5. http://www.anandtech.com/show/10325/the-nvidia-geforce-gtx-1080-and-1070-founders-edition-review/5.

- ↑ Smith, Ryan (July 20, 2016). "The NVIDIA GeForce GTX 1080 & GTX 1070 Founders Editions Review: Kicking Off the FinFET Generation". AnandTech: p. 4. http://www.anandtech.com/show/10325/the-nvidia-geforce-gtx-1080-and-1070-founders-edition-review/4.

- ↑ Harris, Mark (April 5, 2016). "Inside Pascal: NVIDIA's Newest Computing Platform". Parallel Forall. Nvidia. https://devblogs.nvidia.com/parallelforall/inside-pascal/.

- ↑ "NVIDIA TITAN Xp Graphics Card with Pascal Architecture". https://www.nvidia.com/en-us/geforce/products/10series/titan-xp/.

- ↑ "NVIDIA TITAN X Graphics Card with Pascal". GeForce. https://www.nvidia.com/en-us/geforce/products/10series/titan-x-pascal/.

- ↑ "New Quadro Graphics Built on Pascal Architecture". NVIDIA. http://www.nvidia.com/object/quadro-graphics-with-pascal.html.

- ↑ "Accelerating Data Center Workloads with GPUs". NVIDIA. http://www.nvidia.com/object/data-center-solutions.html.

- ↑ "NVIDIA GeForce 10 Series Graphics Cards". https://www.nvidia.com/en-us/geforce/10-series/.

- ↑ "NVIDIA GeForce GTX 1060 to be released on July 7th". 29 June 2016. http://videocardz.com/61583/nvidia-geforce-gtx-1060-to-be-released-on-july-7th.

- ↑ "GTX 1060 Graphics Cards". GeForce. http://www.geforce.com/hardware/10series/geforce-gtx-1060.

- ↑ Smith, Ryan (November 12, 2012). "NVIDIA Launches Tesla K20 & K20X: GK110 Arrives At Last". AnandTech: p. 3. http://www.anandtech.com/show/6446/nvidia-launches-tesla-k20-k20x-gk110-arrives-at-last/3.

- ↑ 29.0 29.1 29.2 29.3 29.4 29.5 Nvidia (September 1, 2015). "CUDA C Programming Guide". http://docs.nvidia.com/cuda/cuda-c-programming-guide/index.html.

- ↑ 30.00 30.01 30.02 30.03 30.04 30.05 30.06 30.07 30.08 30.09 30.10 30.11 30.12 30.13 30.14 Triolet, Damien (May 24, 2016). "Nvidia GeForce GTX 1080, le premier GPU 16nm en test !" (in fr). Hardware.fr: p. 2. http://www.hardware.fr/articles/948-2/gp104-7-2-milliards-transistors-16-nm.html.

- ↑ 31.0 31.1 Smith, Ryan (January 26, 2015). "GeForce GTX 970: Correcting The Specs & Exploring Memory Allocation". AnandTech: p. 1. http://www.anandtech.com/show/8935/geforce-gtx-970-correcting-the-specs-exploring-memory-allocation.

- ↑ "NVIDIA Turing Release Date". Techradar. 2 February 2021. https://www.techradar.com/news/nvidia-turing.

|