Engineering:RISC-V

| Designer | University of California, Berkeley |

|---|---|

| Bits | 32, 64, 128 |

| Version | |

| Design | RISC |

| Type | Load–store |

| Encoding | Variable |

| Branching | Compare-and-branch |

| Endianness | Little[1](p9)[lower-alpha 1] |

| Page size | 4 KiB |

| Extensions |

|

| Open | Yes, royalty free |

| Registers | |

| General purpose |

|

| Floating point |

|

RISC-V[lower-alpha 2] (pronounced "risk-five",[1](p1)) is an open standard instruction set architecture (ISA) based on established reduced instruction set computer (RISC) principles. Unlike most other ISA designs, RISC-V is provided under royalty-free open-source licenses. Many companies are offering or have announced RISC-V hardware; open source operating systems with RISC-V support are available, and the instruction set is supported in several popular software toolchains.

As a RISC architecture, the RISC-V ISA is a load–store architecture. Its floating-point instructions use IEEE 754 floating-point. Notable features of the RISC-V ISA include: instruction bit field locations chosen to simplify the use of multiplexers in a CPU,[1](p17) a design that is architecturally neutral,[dubious ] and a fixed location for the sign bit of immediate values to speed up sign extension.[1](p17)

The instruction set is designed for a wide range of uses. The base instruction set has a fixed length of 32-bit naturally aligned instructions, and the ISA supports variable length extensions where each instruction can be any number of 16-bit parcels in length.[1](pp7-10) Extensions support small embedded systems, personal computers, supercomputers with vector processors, and warehouse-scale parallel computers.

The instruction set specification defines 32-bit and 64-bit address space variants. The specification includes a description of a 128-bit flat address space variant, as an extrapolation of 32- and 64-bit variants, but the 128-bit ISA remains "not frozen" intentionally, because (As of 2023), there is so little practical experience with such large memory systems.[1](p41)

Unlike other academic designs which are typically optimized only for simplicity of exposition, the designers intended that the RISC-V instruction set be usable for practical computers. As of June 2019, version 2.2 of the user-space ISA[4] and version 1.11 of the privileged ISA[2] are frozen, permitting software and hardware development to proceed. The user-space ISA, now renamed the Unprivileged ISA, was updated, ratified and frozen as version 20191213.[1] An external debug specification is available as a draft, version 0.13.2.[5]

The project began in 2010 at the University of California, Berkeley. There are now members in over 70 countries contributing and collaborating to define RISC-V open specifications. RISC-V International, the non-profit managing RISC-V, is currently headquartered in Switzerland .[6][7]

Rationale

CPU design requires design expertise in several specialties: electronic digital logic, compilers, and operating systems. To cover the costs of such a team, commercial vendors of processor intellectual property (IP), such as Arm Ltd. and MIPS Technologies, charge royalties for the use of their designs, patents and copyrights.[8][9][10] They also often require non-disclosure agreements before releasing documents that describe their designs' detailed advantages. In many cases, they never describe the reasons for their design choices.

RISC-V was begun with a goal to make a practical ISA that was open-sourced, usable academically, and deployable in any hardware or software design without royalties.[1](p1)[11] Also, justifying rationales for each design decision of the project are explained, at least in broad terms. The RISC-V authors are academics who have substantial experience in computer design, and the RISC-V ISA is a direct development from a series of academic computer-design projects, especially Berkeley RISC. RISC-V was originated in part to aid all such projects.[1](p1)[11]

To build a large, continuing community of users and thereby accumulate designs and software, the RISC-V ISA designers intentionally support a wide variety of practical use cases: compact, performance, and low-power real-world implementations[1](pp1-2,153-154)[12] without over-architecting for a given microarchitecture.[1](p1)[13][14][15] The requirements of a large base of contributors is part of the reason why RISC-V was engineered to address many possible uses.

The designers' primary assertion is that the instruction set is the key interface in a computer as it is situated at the interface between the hardware and the software. If a good instruction set were open and available for use by all, then it can dramatically reduce the cost of software by enabling far more reuse. It should also trigger increased competition among hardware providers, who can then devote more resources toward design and less for software support.[11]

The designers maintain that new principles are becoming rare in instruction set design, as the most successful designs of the last forty years have grown increasingly similar. Of those that failed, most did so because their sponsoring companies were financially unsuccessful, not because the instruction sets were technically poor. Thus, a well-designed open instruction set designed using well-established principles should attract long-term support by many vendors.[11]

RISC-V also encourages academic usage. The simplicity of the integer subset permits basic student exercises, and is a simple enough ISA to enable software to control research machines. The variable-length ISA provides room for instruction set extensions for both student exercises and research,[1](p7) and the separated privileged instruction set permits research in operating system support without redesigning compilers.[2] RISC-V's open intellectual property paradigm allows derivative designs to be published, reused, and modified.[16]

History

The term RISC dates from about 1980.[17] Before then, there was some knowledge (see John Cocke) that simpler computers can be effective, but the design principles were not widely described. Simple, effective computers have always been of academic interest, and resulted in the RISC instruction set DLX for the first edition of Computer Architecture: A Quantitative Approach in 1990 of which David Patterson was a co-author, and he later participated in the RISC-V origination. DLX was intended for educational use; academics and hobbyists implemented it using field-programmable gate arrays (FPGA), but it was never truly intended for commercial deployment. ARM CPUs, versions 2 and earlier, had a public-domain instruction set and are still supported by the GNU Compiler Collection (GCC), a popular free-software compiler. Three open-source cores exist for this ISA, but were never manufactured.[18][19] OpenRISC is an open-source ISA based on DLX, with associated RISC designs, and is fully supported with GCC and Linux implementations, although it too has few commercial implementations.

Krste Asanović at the University of California, Berkeley, had a research requirement for an open-source computer system, and in 2010, he decided to develop and publish one in a "short, three-month project over the summer" with several of his graduate students. The plan was to aid both academic and industrial users.[11] David Patterson at Berkeley joined the collaboration as he was the originator of the Berkeley RISC,[17] and the RISC-V is the eponymous fifth generation of his long series of cooperative RISC-based research projects at the University of California, Berkeley (RISC-I and RISC-II published in 1981 by Patterson, who refers[20] to the SOAR architecture[21] from 1984 as "RISC-III" and the SPUR architecture[22] from 1988 as "RISC-IV"). At this stage, students provided initial software, simulations, and CPU designs.[23]

The RISC-V authors and their institution originally sourced the ISA documents[24] and several CPU designs under BSD licenses, which allow derivative works—such as RISC-V chip designs—to be either open and free, or closed and proprietary. The ISA specification itself (i.e., the encoding of the instruction set) was published in 2011 as open source,[25] with all rights reserved. The actual technical report (an expression of the specification) was later placed under a Creative Commons license to permit enhancement by external contributors through the RISC-V Foundation, and later RISC-V International.

A full history of RISC-V has been published on the RISC-V International website.[26]

RISC-V Foundation and RISC-V International

Commercial users require an ISA to be stable before they can use it in a product that may last many years. To address this issue, the RISC-V Foundation was formed in 2015 to own, maintain, and publish intellectual property related to RISC-V's definition.[27] The original authors and owners have surrendered their rights to the foundation.[citation needed] The foundation is led by CEO Calista Redmond, who took on the role in 2019 after leading open infrastructure projects at IBM.[28][failed verification]

The founding members of RISC-V were: Andes, Antmicro, Bluespec, CEVA, Codasip, Cortus, Esperanto, Espressif, ETH Zurich, Google, IBM, ICT, IIT Madras, Lattice, lowRISC, Microchip, MIT (Csail), Qualcomm, Rambus, Rumble, SiFive, Syntacore and Technolution.[29]

In November 2019, the RISC-V Foundation announced that it would relocate to Switzerland , citing concerns over U.S. trade regulations.[30][31] As of March 2020, the organization was named RISC-V International, a Swiss nonprofit business association.[32]

Awards

- 2017: The Linley Group's Analyst's Choice Award for Best Technology (for the instruction set)[33]

Design

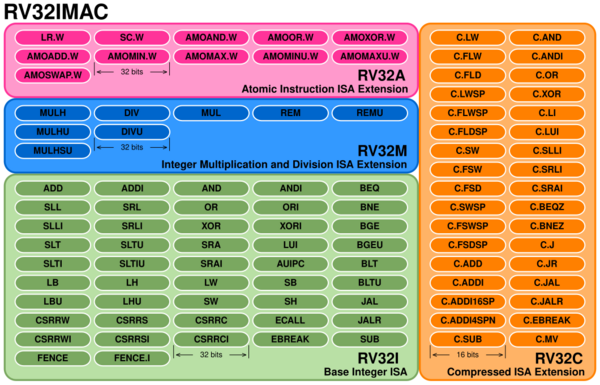

ISA base and extensions

RISC-V has a modular design, consisting of alternative base parts, with added optional extensions. The ISA base and its extensions are developed in a collective effort between industry, the research community and educational institutions. The base specifies instructions (and their encoding), control flow, registers (and their sizes), memory and addressing, logic (i.e., integer) manipulation, and ancillaries. The base alone can implement a simplified general-purpose computer, with full software support, including a general-purpose compiler.

The standard extensions are specified to work with all of the standard bases, and with each other without conflict.

Many RISC-V computers might implement the compressed instructions extension to reduce power consumption, code size, and memory use.[1](pp97-99) There are also future plans to support hypervisors and virtualization.[2]

Together with the supervisor extension, S, an RVGC instruction set, which includes one of the RV base instruction sets, the G collection of extensions (which includes "I", meaning that the base is non-embedded), and the C extension, defines all instructions needed to conveniently support a general purpose operating system.[1](pp129, 154)

| Name | Description | Version | Status[upper-alpha 1] | Instruction count |

|---|---|---|---|---|

| Base | ||||

| RVWMO | Weak Memory Ordering | 2.0 | Ratified | |

| RV32I | Base Integer Instruction Set, 32-bit | 2.1 | Ratified | 40 |

| RV32E | Base Integer Instruction Set (embedded), 32-bit, 16 registers | 2.0 | Ratified | 40 |

| RV64I | Base Integer Instruction Set, 64-bit | 2.1 | Ratified | 15 |

| RV64E | Base Integer Instruction Set (embedded), 64-bit | 2.0 | Ratified | |

| RV128I | Base Integer Instruction Set, 128-bit | 1.7 | Open | 15 |

| Extension | ||||

| M | Standard Extension for Integer Multiplication and Division | 2.0 | Ratified | 8 (RV32) 13 (RV64) |

| A | Standard Extension for Atomic Instructions | 2.1 | Ratified | 11 (RV32) 22 (RV64) |

| F | Standard Extension for Single-Precision Floating-Point | 2.2 | Ratified | 26 (RV32) 30 (RV64) |

| D | Standard Extension for Double-Precision Floating-Point | 2.2 | Ratified | 26 (RV32) 32 (RV64) |

| Zicsr | Control and Status Register (CSR) Instructions | 2.0 | Ratified | 6 |

| Zifencei | Instruction-Fetch Fence | 2.0 | Ratified | 1 |

| G | Shorthand for the IMAFD_Zicsr_Zifencei base and extensions[1](p129) | N/A | N/A | |

| Q | Standard Extension for Quad-Precision Floating-Point | 2.2 | Ratified | 28 (RV32) 32 (RV64) |

| L | Standard Extension for Decimal Floating-Point | 0.0 | Open | |

| C | Standard Extension for Compressed Instructions | 2.0 | Ratified | 40 |

| B | Standard Extension for Bit Manipulation | 1.0 | Ratified | 43[34] |

| J | Standard Extension for Dynamically Translated Languages | 0.0 | Open | |

| T | Standard Extension for Transactional Memory | 0.0 | Open | |

| P | Standard Extension for Packed-SIMD Instructions | 0.9.10 | Open | |

| V | Standard Extension for Vector Operations | 1.0 | Ratified | 187[35] |

| Zk | Standard Extension for Scalar Cryptography | 1.0.1 | Ratified | 49[36] |

| H | Standard Extension for Hypervisor | 1.0 | Ratified | 15 |

| S | Standard Extension for Supervisor-level Instructions | 1.12 | Ratified | 4 |

| Zam | Misaligned Atomics | 0.1 | Open | |

| Zihintpause | Pause Hint | 2.0 | Ratified | |

| Zihintntl | Non-Temporal Locality Hints | 0.3 | Ratified | |

| Zfa | Additional Floating-Point Instructions | 1.0 | Ratified | |

| Zfh | Half-Precision Floating-Point | 1.0 | Ratified | |

| Zfhmin | Minimal Half-Precision Floating-Point | 1.0 | Ratified | |

| Zfinx | Single-Precision Floating-Point in Integer Register | 1.0 | Ratified | |

| Zdinx | Double-Precision Floating-Point in Integer Register | 1.0 | Ratified | |

| Zhinx | Half-Precision Floating-Point in Integer Register | 1.0 | Ratified | |

| Zhinxmin | Minimal Half-Precision Floating-Point in Integer Register | 1.0 | Ratified | |

| Zmmul | Multiplication Subset of the M Extension | 1.0 | Ratified | |

| Ztso | Total Store Ordering | 1.0 | Ratified | |

- ↑ Frozen parts are expected to have their final feature set and to receive only clarifications before being ratified.

| Format | Bit | |||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| Register/register | funct7 | rs2 | rs1 | funct3 | rd | opcode | ||||||||||||||||||||||||||

| Immediate | imm[11:0] | rs1 | funct3 | rd | opcode | |||||||||||||||||||||||||||

| Store | imm[11:5] | rs2 | rs1 | funct3 | imm[4:0] | opcode | ||||||||||||||||||||||||||

| Branch | [12] | imm[10:5] | rs2 | rs1 | funct3 | imm[4:1] | [11] | opcode | ||||||||||||||||||||||||

| Upper immediate | imm[31:12] | rd | opcode | |||||||||||||||||||||||||||||

| Jump | [20] | imm[10:1] | [11] | imm[19:12] | rd | opcode | ||||||||||||||||||||||||||

| ||||||||||||||||||||||||||||||||

To tame the combinations of functions that may be implemented, a nomenclature is defined to specify them in Chapter 27 of the current ratified Unprivileged ISA Specification. The instruction set base is specified first, coding for RISC-V, the register bit-width, and the variant; e.g., RV64I or RV32E. Then follows letters specifying implemented extensions, in the order of the above table. Each letter may be followed by a major optionally followed by "p" and a minor option number. It defaults to 0 if a minor version number is absent, and 1.0 if all of a version number is absent. Thus RV64IMAFD may be written as RV64I1p0M1p0A1p0F1p0D1p0 or more simply as RV64I1M1A1F1D1. Underscores may be used between extensions for readability, for example RV32I2_M2_A2.

The base, extended integer & floating-point calculations, with synchronization primitives for multi-core computing, are considered to be necessary for general-purpose computing, and thus we have the shorthand, "G".

A small 32-bit computer for an embedded system might be RV32EC. A large 64-bit computer might be RV64GC; i.e., RV64IMAFDCZicsr_Zifencei.

With the growth in the number of extensions, the standard now provides for extensions to be named by a single "Z" followed by an alphabetical name and an optional version number. For example, Zifencei names the instruction-fetch extension. Zifencei2 and Zifencei2p0 name version 2.0 of the same. The first letter following the "Z" by convention indicates the most closely related alphabetical extension category, IMAFDQLCBJTPVN. Thus the Zam extension for misaligned atomics relates to the "A" standard extension. Unlike single character extensions, Z extensions must be separated by underscores, grouped by category and then alphabetically within each category. For example, Zicsr_Zifencei_Zam.

Extensions specific to supervisor privilege level are named in the same way using "S" for prefix. Extensions specific to hypervisor level are named using "H" for prefix. Machine level extensions are prefixed with the three letters "Zxm". Supervisor, hypervisor and machine level instruction set extensions are named after less privileged extensions.

RISC-V developers may create their own non-standard instruction set extensions. These follow the "Z" naming convention, but with "X" as the prefix. They should be specified after all standard extensions, and if multiple non-standard extensions are listed, they should be listed alphabetically.

Profiles and Platforms

Profiles and Platforms for standard ISA choice lists are under discussion.

... This flexibility can be used to highly optimize a specialized design by including only the exact set of ISA features required for an application, but the same flexibility also leads to a combinatorial explosion in possible ISA choices. Profiles specify a much smaller common set of ISA choices that capture the most value for most users, and which thereby enable the software community to focus resources on building a rich software ecosystem. [37]

The platform specification defines a set of platforms that specify requirements for interoperability between software and hardware. The Platform Policy defines the various terms used in this platform specification. The platform policy also provides the needed detail regarding the scope, coverage, naming, versioning, structure, life cycle and compatibility claims for the platform specification. [38]

Register sets

| Register name |

Symbolic name |

Description | Saved by |

|---|---|---|---|

| 32 integer registers | |||

| x0 | zero | Always zero | |

| x1 | ra | Return address | Caller |

| x2 | sp | Stack pointer | Callee |

| x3 | gp | Global pointer | |

| x4 | tp | Thread pointer | |

| x5 | t0 | Temporary / alternate return address | Caller |

| x6–7 | t1–2 | Temporaries | Caller |

| x8 | s0/fp | Saved register / frame pointer | Callee |

| x9 | s1 | Saved register | Callee |

| x10–11 | a0–1 | Function arguments / return values | Caller |

| x12–17 | a2–7 | Function arguments | Caller |

| x18–27 | s2–11 | Saved registers | Callee |

| x28–31 | t3–6 | Temporaries | Caller |

| 32 floating-point extension registers | |||

| f0–7 | ft0–7 | Floating-point temporaries | Caller |

| f8–9 | fs0–1 | Floating-point saved registers | Callee |

| f10–11 | fa0–1 | Floating-point arguments/return values | Caller |

| f12–17 | fa2–7 | Floating-point arguments | Caller |

| f18–27 | fs2–11 | Floating-point saved registers | Callee |

| f28–31 | ft8–11 | Floating-point temporaries | Caller |

RISC-V has 32 integer registers (or 16 in the embedded variant),[1](pp13, 33) and when the floating-point extension is implemented, an additional 32 floating-point registers.[1](p63) Except for memory access instructions, instructions address only registers.

The first integer register is a zero register, and the remainder are general-purpose registers. A store to the zero register has no effect, and a read always provides 0. Using the zero register as a placeholder makes for a simpler instruction set.

Control and status registers exist, but user-mode programs can access only those used for performance measurement and floating-point management.

No instructions exist to save and restore multiple registers. Those were thought to be needless, too complex, and perhaps too slow.[16]

Memory access

Like many RISC designs, RISC-V is a load–store architecture: instructions address only registers, with load and store instructions conveying data to and from memory.

Most load and store instructions include a 12-bit offset and two register identifiers. One register is the base register. The other register is the destination (for a load) or the source (for a store).

The offset is added to a base register to get the address.[1](p24) Forming the address as a base register plus offset allows single instructions to access data structures. For example, if the base register points to the top of a stack, single instructions can access a subroutine's local variables in the stack. Likewise the load and store instructions can access a record-style structure or a memory-mapped I/O device. Using the constant zero register as a base address allows single instructions to access memory near address zero.

Memory is addressed as 8-bit bytes, with instructions being in little-endian order,[1](pp9-10) and with data being in the byte order defined by the execution environment interface in which code is running.[1](pp3,9-10,24) Words, up to the register size, can be accessed with the load and store instructions.

RISC-V was originally specified as little-endian to resemble other familiar, successful computers, for example, x86.[1](pp9-10) This also reduces a CPU's complexity and costs slightly less because it reads all sizes of words in the same order. For example, the RISC-V instruction set decodes starting at the lowest-addressed byte of the instruction. Big-endian and bi-endian variants were defined for support of legacy code bases that assume big-endianness.[1](pp9-10) The privileged ISA defines bits in the mstatus and mstatush registers that indicate and, optionally, control whether M-mode, S-mode, and U-mode memory accesses other than instruction fetches are little-endian or big-endian; those bits may be read-only, in which case the endianness of the implementation is hardwired, or may be writable.[2]:23–24

An execution environment interface may allow accessed memory addresses not to be aligned to their word width, but accesses to aligned addresses may be faster; for example, simple CPUs may implement unaligned accesses with slow software emulation driven from an alignment failure interrupt.[1](pp3,24-25)

Like many RISC instruction sets (and some complex instruction set computer (CISC) instruction sets, such as x86 and IBM System/360 and its successors through z/Architecture), RISC-V lacks address-modes that write back to the registers. For example, it does not auto-increment.[1](p24)

RISC-V manages memory systems that are shared between CPUs or threads by ensuring a thread of execution always sees its memory operations in the programmed order. But between threads and I/O devices, RISC-V is simplified: it doesn't guarantee the order of memory operations, except by specific instructions, such as fence.

A fence instruction guarantees that the results of predecessor operations are visible to successor operations of other threads or I/O devices. fence can guarantee the order of combinations of both memory and memory-mapped I/O operations. E.g. it can separate memory read and write operations, without affecting I/O operations. Or, if a system can operate I/O devices in parallel with memory, fence doesn't force them to wait for each other. One CPU with one thread may decode fence as nop.

Some RISC CPUs (such as MIPS, PowerPC, DLX, and Berkeley's RISC-I) place 16 bits of offset in the loads and stores. They set the upper 16 bits by a load upper word instruction. This permits upper-halfword values to be set easily, without shifting bits. However, most use of the upper half-word instruction makes 32-bit constants, like addresses. RISC-V uses a SPARC-like combination of 12-bit offsets and 20-bit set upper instructions. The smaller 12-bit offset helps compact, 32-bit load and store instructions select two of 32 registers yet still have enough bits to support RISC-V's variable-length instruction coding.[1](p16)

Immediates

RISC-V handles 32-bit constants and addresses with instructions that set the upper 20 bits of a 32-bit register. Load upper immediate lui loads 20 bits into bits 31 through 12. Then a second instruction such as addi can set the bottom 12 bits. Small numbers or addresses can be formed by using the zero register instead of lui.

This method is extended to permit position-independent code by adding an instruction, auipc that generates 20 upper address bits by adding an offset to the program counter and storing the result into a base register. This permits a program to generate 32-bit addresses that are relative to the program counter.

The base register can often be used as-is with the 12-bit offsets of the loads and stores. If needed, addi can set the lower 12 bits of a register. In 64-bit and 128-bit ISAs,lui and auipc sign-extend the result to get the larger address.[1](p37)

Some fast CPUs may interpret combinations of instructions as single fused instructions. lui or auipc are good candidates to fuse with jalr, addi, loads or stores.

Subroutine calls, jumps, and branches

RISC-V's subroutine call jal (jump and link) places its return address in a register. This is faster in many computer designs, because it saves a memory access compared to systems that push a return address directly on a stack in memory. jal has a 20-bit signed (two's complement) offset. The offset is multiplied by 2, then added to the PC to generate a relative address to a 32-bit instruction. If the result is not at a 32-bit address (i.e., evenly divisible by 4), the CPU may force an exception.[1](pp20–23)

RISC-V CPUs jump to calculated addresses using a jump and link-register, jalr instruction. jalr is similar to jal, but gets its destination address by adding a 12-bit offset to a base register. (In contrast,jal adds a larger 20-bit offset to the PC.)

jalr's bit format is like the register-relative loads and stores. Like them, jalr can be used with the instructions that set the upper 20 bits of a base register to make 32-bit branches, either to an absolute address (using lui) or a PC-relative one (using auipc for position-independent code). (Using a constant zero base address allows single-instruction calls to a small (the offset), fixed positive or negative address.)

RISC-V recycles jal and jalr to get unconditional 20-bit PC-relative jumps and unconditional register-based 12-bit jumps. Jumps just make the linkage register 0 so that no return address is saved.[1](pp20–23)

RISC-V also recycles jalr to return from a subroutine: To do this, jalr's base register is set to be the linkage register saved by jal or jalr. jalr's offset is zero and the linkage register is zero, so that there is no offset, and no return address is saved.

Like many RISC designs, in a subroutine call, a RISC-V compiler must use individual instructions to save registers to the stack at the start, and then restore these from the stack on exit. RISC-V has no save multiple or restore multiple register instructions. These were thought to make the CPU too complex, and possibly slow.[39] This can take more code space. Designers planned to reduce code size with library routines to save and restore registers.[40]

RISC-V has no condition code register or carry bit. The designers believed that condition codes make fast CPUs more complex by forcing interactions between instructions in different stages of execution. This choice makes multiple-precision arithmetic more complex. Also, a few numerical tasks need more energy. As a result, predication (the conditional execution of instructions) is not supported. The designers claim that very fast, out-of-order CPU designs do predication anyway, by doing the comparison branch and conditional code in parallel, then discarding the unused path's effects. They also claim that even in simpler CPUs, predication is less valuable than branch prediction, which can prevent most stalls associated with conditional branches. Code without predication is larger, with more branches, but they also claim that a compressed instruction set (such as RISC-V's set C) solves that problem in most cases.[16][failed verification]

Instead, RISC-V has short branches that perform comparisons: equal, not-equal, less-than, unsigned less-than, greater-than or equal and unsigned greater-than or equal. Ten comparison-branch operations are implemented with only six instructions, by reversing the order of operands in the assembler. For example, branch if greater than can be done by less-than with a reversed order of operands.[1](pp20–23)

The comparing branches have a twelve-bit signed range, and jump relative to the PC.[1](pp20–23)

Unlike some RISC architectures, RISC-V does not include a branch delay slot, a position after a branch instruction that can be filled with an instruction that is executed whether or not the branch is taken.[1](pp20–23) RISC-V omits a branch delay slot because it complicates multicycle CPUs, superscalar CPUs, and long pipelines. Dynamic branch predictors have succeeded well enough to reduce the need for delayed branches.[16]

On the first encounter with a branch, RISC-V CPUs should assume that a negative relative branch (i.e. the sign bit of the offset is "1") will be taken.[1](pp20–23) This assumes that a backward branch is a loop, and provides a default direction so that simple pipelined CPUs can fill their pipeline of instructions. Other than this, RISC-V does not require branch prediction, but core implementations are allowed to add it. RV32I reserves a "HINT" instruction space that presently does not contain any hints on branches;[1](pp28–29) RV64I does the same.[1](pp38–39)

Arithmetic and logic sets

RISC-V segregates math into a minimal set of integer instructions (set I) with add, subtract, shift, bitwise logic and comparing-branches. These can simulate most of the other RISC-V instruction sets with software. (The atomic instructions are a notable exception.) RISC-V integer instructions lacks the count leading zero and bit-field operations normally used to speed software floating-point in a pure-integer processor, However, while nominally in the bit manipulation extension, the ratified Zbb, Zba and Zbs extensions contain further integer instructions including a count leading zero instruction.

The integer multiplication instructions (set M) include signed and unsigned multiply and divide. Double-precision integer multiplies and divides are included, as multiplies and divides that produce the high word of the result. The ISA document recommends that implementors of CPUs and compilers fuse a standardized sequence of high and low multiply and divide instructions to one operation if possible.[1](pp43-45)

The floating-point instructions (set F) include single-precision arithmetic and also comparison-branches similar to the integer arithmetic. It requires an additional set of 32 floating-point registers. These are separate from the integer registers. The double-precision floating point instructions (set D) generally assume that the floating-point registers are 64-bit (i.e., double-width), and the F subset is coordinated with the D set. A quad-precision 128-bit floating-point ISA (Q) is also defined.[1](pp63-82) RISC-V computers without floating-point can use a floating-point software library.

RISC-V does not cause exceptions on arithmetic errors, including overflow,[1](pp17-20) underflow, subnormal, and divide by zero.[1](pp44-45) Instead, both integer and floating-point arithmetic produce reasonable default values, and floating-point instructions set status bits.[1](p66) Divide-by-zero can be discovered by one branch after the division.[1](pp44-45) The status bits can be tested by an operating system or periodic interrupt.

Atomic memory operations

RISC-V supports computers that share memory between multiple CPUs and threads. RISC-V's standard memory consistency model is release consistency. That is, loads and stores may generally be reordered, but some loads may be designated as acquire operations which must precede later memory accesses, and some stores may be designated as release operations which must follow earlier memory accesses.[1](pp83-94)

The base instruction set includes minimal support in the form of a fence instruction to enforce memory ordering.[1](pp26-27) Although this is sufficient (fence r, rw provides acquire and fence rw, w provides release), combined operations can be more efficient.[1](Chapter 8)

The atomic memory operation extension supports two types of atomic memory operations for release consistency. First, it provides general purpose load-reserved lr and store-conditional sc instructions. lr performs a load, and tries to reserve that address for its thread. A later store-conditional sc to the reserved address will be performed only if the reservation is not broken by an intervening store from another source. If the store succeeds, a zero is placed in a register. If it failed, a non-zero value indicates that software needs to retry the operation. In either case, the reservation is released.[1](Chapter 8)

The second group of atomic instructions perform read-modify-write sequences: a load (which is optionally a load-acquire) to a destination register, then an operation between the loaded value and a source register, then a store of the result (which may optionally be a store-release). Making the memory barriers optional permits combining the operations. The optional operations are enabled by acquire and release bits which are present in every atomic instruction. RISC-V defines nine possible operations: swap (use source register value directly); add; bitwise and, or, and exclusive-or; and signed and unsigned minimum and maximum.[1](Chapter 8)

A system design may optimize these combined operations more than lr and sc. For example, if the destination register for a swap is the constant zero, the load may be skipped. If the value stored is unmodified since the load, the store may be skipped.[4](p44)

The IBM System/370 and its successors including z/Architecture, and x86, both implement a compare-and-swap (cas) instruction, which tests and conditionally updates a location in memory: if the location contains an expected old value, cas replaces it with a given new value; it then returns an indication of whether it made the change. However, a simple load-type instruction is usually performed before the cas to fetch the old value. The classic problem is that if a thread reads (loads) a value A, calculates a new value C, and then uses (cas) to replace A with C, it has no way to know whether concurrent activity in another thread has replaced A with some other value B and then restored the A in between. In some algorithms (e.g., ones in which the values in memory are pointers to dynamically allocated blocks), this ABA problem can lead to incorrect results. The most common solution employs a double-wide cas instruction to update both the pointer and an adjacent counter; unfortunately, such an instruction requires a special instruction format to specify multiple registers, performs several reads and writes, and can have complex bus operation.[1](pp48-49)

The lr/sc alternative is more efficient. It usually requires only one memory load, and minimizing slow memory operations is desirable. It's also exact: it controls all accesses to the memory cell, rather than just assuring a bit pattern. However, unlike cas, it can permit livelock, in which two or more threads repeatedly cause each other's instructions to fail. RISC-V guarantees forward progress (no livelock) if the code follows rules on the timing and sequence of instructions: 1) It must use only the I subset. 2) To prevent repetitive cache misses, the code (including the retry loop) must occupy no more than 16 consecutive instructions. 3) It must include no system or fence instructions, or taken backward branches between the lr and sc. 4) The backward branch to the retry loop must be to the original sequence.[1](pp48-49)

The specification gives an example of how to use the read-modify-write atomic instructions to lock a data structure.[1](p54)

Compressed subset

The standard RISC-V ISA specifies that all instructions are 32 bits. This makes for a particularly simple implementation, but like other RISC processors with 32-bit instruction encoding, results in larger code size than in instruction sets with variable-length instructions.[1](p99)[39]

To compensate, RISC-V's 32-bit instructions are actually 30 bits; 3⁄4 of the opcode space is reserved for an optional (but recommended) variable-length compressed instruction set, RVC, that includes 16-bit instructions. As in ARM Thumb and MIPS16, the compressed instructions are simply alternative encodings for a subset of the larger instructions. Unlike the ARM or MIPS compressed sets, space was reserved from the start so there is no separate operating mode. Standard and compressed instructions may be intermixed freely.[1](p97)[39] (Extension letter is C.)[1](p97)

Because (like Thumb-1 and MIPS16) the compressed instructions are simply alternate encodings (aliases) for a selected subset of larger instructions, the compression can be implemented in the assembler, and it is not essential for the compiler to even know about it.

A prototype of RVC was tested in 2011.[39] The prototype code was 20% smaller than an x86 PC and MIPS compressed code, and 2% larger than ARM Thumb-2 code.[39] It also substantially reduced both the needed cache memory and the estimated power use of the memory system.[39]

The researcher intended to reduce the code's binary size for small computers, especially embedded computer systems. The prototype included 33 of the most frequently used instructions, recoded as compact 16-bit formats using operation codes previously reserved for the compressed set.[39] The compression was done in the assembler, with no changes to the compiler. Compressed instructions omitted fields that are often zero, used small immediate values or accessed subsets (16 or 8) of the registers. addi is very common and often compressible.[39]

Much of the difference in size compared to ARM's Thumb set occurred because RISC-V, and the prototype, have no instructions to save and restore multiple registers. Instead, the compiler generated conventional instructions that access the stack. The prototype RVC assembler then often converted these to compressed forms that were half the size. However, this still took more code space than the ARM instructions that save and restore multiple registers. The researcher proposed to modify the compiler to call library routines to save and restore registers. These routines would tend to remain in a code cache and thus run fast, though probably not as fast as a save-multiple instruction.[39]

Standard RVC requires occasional use of 32-bit instructions. Several nonstandard RVC proposals are complete, requiring no 32-bit instructions, and are said to have higher densities than standard RVC.[41][42] Another proposal builds on these, and claims to use less coding range as well.[43]

Embedded subset

An instruction set for the smallest embedded CPUs (set E) is reduced in other ways: Only 16 of the 32 integer registers are supported.[1](Chapter 4) All current extensions may be used; a floating-point extension to use the integer registers for floating-point values is being considered. The privileged instruction set supports only machine mode, user mode and memory schemes that use base-and-bound address relocation.[2]

Discussion has occurred for a microcontroller profile for RISC-V, to ease development of deeply embedded systems. It centers on faster, simple C-language support for interrupts, simplified security modes and a simplified POSIX application binary interface.[44]

Correspondents have also proposed smaller, non-standard, 16-bit RV16E ISAs: Several serious proposals would use the 16-bit C instructions with 8 × 16-bit registers.[42][41] An April fools' joke proposed a very practical arrangement: Utilize 16 × 16-bit integer registers, with the standard EIMC ISAs (including 32-bit instructions.) The joke was to use bank switching when a 32-bit CPU would be clearly superior with the larger address space.[45]

Privileged instruction set

RISC-V's ISA includes a separate privileged instruction set specification, which mostly describes three privilege levels plus an orthogonal hypervisor mode. (As of December 2021), version 1.12 is ratified by RISC-V International.[2]

Version 1.12 of the specification supports several types of computer systems:

- Systems that have only machine mode, perhaps for simple embedded systems,

- Systems with both machine mode (for a simple supervisor) and user-mode to implement relatively secure embedded systems,

- Systems with machine-mode, supervisor mode (for operating system) and user-modes for typical operating systems.

These correspond roughly to systems with up to four rings of privilege and security, at most: machine, hypervisor, supervisor and user. Each layer also is expected to have a thin layer of standardized supporting software that communicates to a more-privileged layer, or hardware.[2]

The ISA also includes a hypervisor mode that is orthogonal to the user and supervisor modes.[46] The basic feature is a configuration bit that either permits supervisor-level code to access hypervisor registers, or causes an interrupt on accesses. This bit lets supervisor mode directly handle the hardware needed by a hypervisor. This simplifies the implementation of hypervisors that are hosted by an operating system. This is a popular mode to run warehouse-scale computers. To support non-hosted hypervisors, the bit can cause these accesses to interrupt to a hypervisor. The design also simplifies nesting of hypervisors, in which a hypervisor runs under a hypervisor, and if necessary it lets the kernel use hypervisor features within its own kernel code. As a result, the hypervisor form of the ISA supports five modes: machine, supervisor, user, supervisor-under-hypervisor and user-under-supervisor.

The privileged instruction set specification explicitly defines hardware threads, or harts. Multiple hardware threads are a common practice in more-capable computers. When one thread is stalled, waiting for memory, others can often proceed. Hardware threads can help make better use of the large number of registers and execution units in fast out-of-order CPUs. Finally, hardware threads can be a simple, powerful way to handle interrupts: No saving or restoring of registers is required, simply executing a different hardware thread. However, the only hardware thread required in a RISC-V computer is thread zero.[2]

Interrupts and exceptions are handled together. Exceptions are caused by instruction execution including illegal instructions and system calls, while interrupts are caused by external events. The existing control and status register definitions support RISC-V's error and memory exceptions, and a small number of interrupts, typically via an "advanced core local interruptor" (ACLINT).[47] For systems with more interrupts, the specification also defines a platform-level interrupt controller (PLIC) to coordinate large number of interrupts among multiple processors. Interrupts always start at the highest-privileged machine level, and the control registers of each level have explicit forwarding bits to route interrupts to less-privileged code. For example, the hypervisor need not include software that executes on each interrupt to forward an interrupt to an operating system. Instead, on set-up, it can set bits to forward the interrupt.[2]

Several memory systems are supported in the specification. Physical-only is suited to the simplest embedded systems. There are also four UNIX-style virtual memory systems for memory cached in mass-storage systems. The virtual memory systems support MMU with four sizes, with addresses sized 32, 39, 48 and 57 bits. All virtual memory systems support 4 KiB pages, multilevel page-table trees and use very similar algorithms to walk the page table trees. All are designed for either hardware or software page-table walking. To optionally reduce the cost of page table walks, super-sized pages may be leaf pages in higher levels of a system's page table tree. SV32 is only supported on 32-bit implementations, has a two-layer page table tree and supports 4 MiB superpages. SV39 has a three level page table, and supports 2 MiB superpages and 1 GiB gigapages. SV48 is required to support SV39. It also has a 4-level page table and supports 2 MiB superpages, 1 GiB gigapages, and 512 GiB terapages. SV57 has a 5-level page table and supports 2 MiB superpages, 1 GiB gigapages, 512 GiB terapages and 256 TiB petapages. Superpages are aligned on the page boundaries for the next-lowest size of page.[2]

Bit manipulation

Some bit-manipulation ISA extensions were ratified in November 2021 (Zba, Zbb, Zbc, Zbs).[34] The Zba, Zbb, and Zbs extensions are arguably extensions of the standard I integer instructions: Zba contains instructions to speed up the computation of the addresses of array elements in arrays of datatypes of size 2, 4, or 8 bytes (sh1add, sh2add, sh3add), and for 64 (and 128) bit processors when indexed with unsigned integers (add.uw, sh1add.uw, sh2add.uw, sh3add.uw and slli.uw). The Zbb instructions contains operations to count leading, trailing 0 bits or all 1 bits in a full and 32 word operations (clz, clzw, ctz, ctzw, cpop, cpopw), byte order reversion (rev8), logical instructions with negation of the second input (andn,orn, xnor), sign and zero extension (sext.b, sext.h, zext.h) that could not be provided as special cases of other instructions (andi, addiw, add.wu), min and max of (signed and unsigned) integers, (left and right) rotation of bits in a register and 32-bit words (rori,roriw, ror, rorw, rol, rolw), and a byte wise "or combine" operation which allows detection of a zero byte in a full register, useful for handling C-style null terminated strings functions. The Zbs extension allows setting, getting, clearing, and toggling individual bits in a register by their index (bseti, bset, bexti, bext, bclri, bclr, binvi,binv).

The Zbc extension has instructions for "carryless multiplication", which does the multiplication of polynomials over the Galois field GF(2) (clmul, clmulh, clmulr). These are useful for cryptography and CRC checks of data integrity.

Done well, a more specialised bit-manipulation subset can aid cryptographic, graphic, and mathematical operations. Further instructions that have been discussed include instructions to shift in ones, a generalized bit-reverse, shuffle and crossbar permutations, bit-field place, extract and deposit pack two words, bytes or halfwords in one register, CRC instructions, bit-matrix operations (RV64 only), conditional mix, conditional move, funnel shifts. The criteria for inclusion documented in the draft were compliant with RISC-V philosophies and ISA formats, substantial improvements in code density or speed (i.e., at least a 3-for-1 reduction in instructions), and substantial real-world applications, including preexisting compiler support. Version 0.93 of the bit-manipulation extension includes those instructions;[48] some of them are now in version 1.0.1 of the Scalar and Entropy Source instructions cryptography extension.[36]

Packed SIMD

Packed-SIMD instructions are widely used by commercial CPUs to inexpensively accelerate multimedia and other digital signal processing.[16] For simple, cost-reduced RISC-V systems, the base ISA's specification proposed to use the floating-point registers' bits to perform parallel single instruction, multiple data (SIMD) sub-word arithmetic.

In 2017 a vendor published a more detailed proposal to the mailing list, and this can be cited as version 0.1.[49] (As of 2019), the efficiency of this proposed ISA varies from 2x to 5x a base CPU for a variety of DSP codecs.[50] The proposal lacked instruction formats and a license assignment to RISC-V International, but it was reviewed by the mailing list.[49] Some unpopular parts of this proposal were that it added a condition code, the first in a RISC-V design, linked adjacent registers (also a first), and has a loop counter that can be difficult to implement in some microarchitectures.

Vector set

The proposed vector-processing instruction set may make the packed SIMD set obsolete. The designers hope to have enough flexibility that a CPU can implement vector instructions in a standard processor's registers. This would enable minimal implementations with similar performance to a multimedia ISA, as above. However, a true vector coprocessor could execute the same code with higher performance.[51]

(As of September 2021), the vector extension is at version 1.0.[52] It is a conservative, flexible design of a general-purpose mixed-precision vector processor, suitable to execute compute kernels. Code would port easily to CPUs with differing vector lengths, ideally without recompiling.[51]

In contrast, short-vector SIMD extensions are less convenient. These are used in x86, ARM and PA-RISC. In these, a change in word-width forces a change to the instruction set to expand the vector registers (in the case of x86, from 64-bit MMX registers to 128-bit Streaming SIMD Extensions (SSE), to 256-bit Advanced Vector Extensions (AVX), and AVX-512). The result is a growing instruction set, and a need to port working code to the new instructions.

In the RISC-V vector ISA, rather than fix the vector length in the architecture, instructions (vsetvli, vsetivli, and vsetvl) are available which take a requested size and sets the vector length to the minimum of the hardware limit and the requested size. So, the RISC-V proposal is more like a Cray's long-vector design or ARM's Scalable Vector Extension. That is, each vector in up to 32 vectors is the same length.[52]:25

The application specifies the total vector width it requires, and the processor determines the vector length it can provide with available on-chip resources. This takes the form of an instruction (vsetcfg) with four immediate operands, specifying the number of vector registers of each available width needed. The total must be no more than the addressable limit of 32, but may be less if the application does not require them all. The vector length is limited by the available on-chip storage divided by the number of bytes of storage needed for each entry. (Added hardware limits may also exist, which in turn may permit SIMD-style implementations.)[51]

Outside of vector loops, the application can zero the number of requested vector registers, saving the operating system the work of preserving them on context switches.[51]

The vector length is not only architecturally variable, but designed to vary at run time also. To achieve this flexibility, the instruction set is likely to use variable-width data paths and variable-type operations using polymorphic overloading.[51] The plan is that these can reduce the size and complexity of the ISA and compiler.[51]

Recent experimental vector processors with variable-width data paths also show profitable increases in operations per: second (speed), area (lower cost), and watt (longer battery life).[53]

Unlike a typical modern graphics processing unit, there are no plans to provide special hardware to support branch predication. Instead, lower cost compiler-based predication will be used.[51][54]

External debug system

There is a preliminary specification for RISC-V's hardware-assisted debugger. The debugger will use a transport system such as Joint Test Action Group (JTAG) or Universal Serial Bus (USB) to access debug registers. A standard hardware debug interface may support either a standardized abstract interface or instruction feeding.[55][56]

(As of January 2017), the exact form of the abstract interface remains undefined, but proposals include a memory mapped system with standardized addresses for the registers of debug devices or a command register and a data register accessible to the communication system.[55] Correspondents claim that similar systems are used by Freescale's background debug mode interface (BDM) for some CPUs, ARM, OpenRISC, and Aeroflex's LEON.[55]

In instruction feeding, the CPU will process a debug exception to execute individual instructions written to a register. This may be supplemented with a data-passing register and a module to directly access the memory. Instruction feeding lets the debugger access the computer exactly as software would. It also minimizes changes in the CPU, and adapts to many types of CPU. This was said to be especially apt for RISC-V because it is designed explicitly for many types of computers. The data-passing register allows a debugger to write a data-movement loop to RAM, and then execute the loop to move data into or out of the computer at a speed near the maximum speed of the debug system's data channel.[55] Correspondents say that similar systems are used by MIPS Technologies MIPS, Intel Quark, Tensilica's Xtensa, and for Freescale Power ISA CPUs' background debug mode interface (BDM).[55]

A vendor proposed a hardware trace subsystem for standardization, donated a conforming design, and initiated a review.[57][58] The proposal is for a hardware module that can trace code execution on most RISC-V CPUs. To reduce the data rate, and permit simpler or less-expensive paths for the trace data, the proposal does not generate trace data that can be calculated from a binary image of the code. It sends only data that indicates "uninferrable" paths through the program, such as which conditional branches are taken. To reduce the data rates, branches that can be calculated, such as unconditional branches, are not traced. The proposed interface between the module and the control unit is a logic signal for each uninferrable type of instruction. Addresses and other data are to be provided in a specialized bus attached to appropriate data sources in a CPU. The data structure sent to an external trace unit is a series of short messages with the needed data. The details of the data channel are intentionally not described in the proposal, because several are likely to make sense.

Implementations

The RISC-V organization maintains a list of RISC-V CPU and SoC implementations.[59]

Existing

Existing proprietary implementations include:

- Allwinner Technology has implemented the XuanTie C906 CPU into their D1 Application Processor.[60]

- Andes Technology Corporation, a Founding Premier member of RISC-V International.[61] Its RISC-V CPU families range from tiny 32-bit cores to advanced 64-bit cores with DSP, FPU, vector, superscalar, and/or multicore capabilities.

- Bouffalo Lab has a series of MCUs based on RISC-V (RV32IMACF, BL60x/BL70x series).[62]

- CloudBEAR is a processor IP company that develops its own RISC-V cores for a range of applications.[63]

- Codasip, a founding member of RISC-V International,[61] has developed a range of low-power embedded, high-performance embedded and application processor cores.[64][65]

- Cortus, an original founding Platinum member of the RISC-V foundation and the RISC-V International,[61] has several RISC-V implementations. Cortus offers ASIC design services using its large IP portfolio including RISC-V 32/64-bit processors from low-end to very high performance RISC-V OoO processors, digital, analog, RF, security and a complete IDE/toolchain/debug eco-system.

- Espressif added a RISC-V ULP coprocessor to their ESP32-S2 microcontroller.[66] In November 2020 Espressif announced their ESP32-C3, a single-core, 32-bit, RISC-V (RV32IMC) based MCU.[67]

- Fraunhofer IPMS was the first organization to develop a RISC-V core that can meet functional safety requirements. The IP Core EMSA5 is a 32-bit processor with a five-stage pipeline and is available as a general purpose variant (EMSA5-GP) and as a safety variant (EMSA5-FS) that can meet an ISO 26262 Automotive Safety Integrity Level-D standard.[68]

- GigaDevice has a series of MCUs based on RISC-V (RV32IMAC, GD32V series),[69] with one of them used on the Longan Nano board produced by a Chinese electronic company Sipeed.[70]

- Google has developed the Titan M2 security module for the Pixel 6 and Pixel 7[71]

- GreenWaves Technologies announced the availability of GAP8, a 32-bit 1 controller plus 8 compute cores, 32-bit SoC (RV32IMC) and developer board in February 2018. Their GAPuino GAP8 development board started shipping in May 2018.[72][73][74]

- Imagination Technologies RTXM-2200[75] is the first core from their Catapult range. It’s a real-time, deterministic, 32-bit embedded CPU

- Instant SoC RISC-V cores from FPGA cores. System on chip, including RISC-V cores, defined by C++.

- Micro Magic Inc. announced the world's fastest 64-bit RISC-V core achieving 5 GHz and 13,000 CoreMarks in October 2020.

- MIPS pivoted to developing RISC-V cores in 2021. It rolled out its first implementation eVocore P8700 in December 2022.[76][77]

- Seagate, in December 2020 announced that it had developed two RISC-V general-purpose cores for use in upcoming controllers for its storage devices.[78]

- SiFive, a company established specifically for developing RISC-V hardware, has processor models released in 2017.[79][80] These include a quad-core, 64-bit (RV64GC) system on a chip (SoC) capable of running general-purpose operating systems such as Linux.[81]

- StarFive, an offshoot of SiFive based in China, offers two RISC-V implementations – one for big data applications and the other for computational storage.[82][83]

- Syntacore,[84] a founding member of RISC-V International and one of the first commercial RISC-V IP vendors, develops and licenses family of RISC-V IP since 2015. (As of 2018), product line includes eight 32- and 64-bit cores, including open-source SCR1 MCU core (RV32I/E[MC]).[85] First commercial SoCs, based on the Syntacore IP were demonstrated in 2016.[86]

- WinChipHead (WCH), a Chinese semiconductor manufacturer of popular and inexpensive USB chips such as CH340 and ARM microcontrollers[87] introduced a simple, inexpensive RISC-V microcontroller line CH32Vxxx, headed by US$0.10 CH32V003.[88][89]

- Codasip and UltraSoC have developed fully supported intellectual property for RISC-V embedded SOCs that combine Codasip's RISC-V cores and other IP with UltraSoC's debug, optimization and analytics.[90]

- As of 2020, the Indian defence and strategic sector started using the 64-bit RISC-V based 100-350 MHz Risecreek processor[citation needed] developed by IIT-Madras which is fabricated by Intel with 22 nm FinFET process.[91][92]

In development

- ASTC developed a RISC-V CPU for embedded ICs.[93]

- Centre for Development of Advanced Computing (C-DAC) in India is developing a single core 32-bit in-order, a single core 64-bit in-order and three out-of-order single, dual and quad-core RISC-V processor under VEGA Microprocessors series.[94][95][96]

- Cobham Gaisler NOEL-V 64-bit.[97]

- Computer Laboratory, University of Cambridge, in collaboration with the FreeBSD Project, has ported that operating system to 64-bit RISC-V to use as a hardware-software research platform.[98]

- Esperanto Technologies announced that they are developing three RISC-V based processors: the ET-Maxion high-performance core, ET-Minion energy-efficient core, and ET-Graphics graphics processor.[99]

- Esperanto ET-SoC-1, a 200 TOPS "kilocore" supercomputer on a chip, with 1088 small 64-bit in-order ET-Minion cores with tensor/vector units and 4 big 64-bit out-of-order ET-Maxion cores[100]

- ETH Zurich and the University of Bologna have cooperatively developed the open-source RISC-V PULPino processor[101] as part of the Parallel Ultra-Low Power (PULP) project for energy-efficient IoT computing.[102]

- European Processor Initiative (EPI), RISC-V Accelerator Stream.[103][104]

Illustration of EPI's first working RISC-V chip sample in 2021.

Illustration of EPI's first working RISC-V chip sample in 2021. - Reconfigurable Intelligent Systems Engineering Group (RISE) of IIT-Madras is developing six Shakti series RISC-V open-source CPU designs for six distinct uses, from a small 32-bit CPU for the Internet of things (IoT) to large, 64-bit CPUs designed for warehouse-scale computers such as server farms based on RapidIO and Hybrid Memory Cube technologies.[105][14][106] 32-bit Moushik successfully booted by RISE for the application of credit cards, electronic voting machines (EVMs), surveillance cameras, safe locks, personalized health management systems.[92][107]

- lowRISC is a non profit project to implement a fully open-source hardware system on a chip (SoC) based on the 64-bit RISC-V ISA.[108]

- Nvidia plans to use RISC-V to replace their Falcon processor on their GeForce graphics cards.[109]

- RV64X consortium is working on a set of graphics extensions to RISC-V and has announced that they are developing an open source RISC-V core with a GPU unit.[110]

- SiFive announced their first RISC-V out-of-order high performance CPU core, the U8 Series Processor IP.[111]

- Ventana revealed they are developing high performance RISC-V CPU IP and chiplet technology targeting data center applications.[112][113]

Open source

Many open-sourced RISC-V CPU designs exist, including:

- The Berkeley CPUs. These are implemented in a unique hardware design language, Chisel, and some are named for famous train engines:

- 64-bit Rocket.[114] Rocket may suit compact, low-power intermediate computers such as personal devices. Named for Stephenson's Rocket.

- The 64-bit Berkeley Out of Order Machine (BOOM).[115] The Berkeley Out-of-Order Machine (BOOM) is a synthesizable and parameterizable open source RV64GC RISC-V core written in the Chisel hardware construction language. BOOM uses much of the infrastructure created for Rocket, and may be usable for personal, supercomputer, and warehouse-scale computers.

- Five 32-bit Sodor CPU designs from Berkeley, designed for student projects.[13] Sodor is the fictional island of trains in children's stories about Thomas the Tank Engine.

- PicoRV32 by Claire Wolf,[116] a 32-bit microcontroller unit (MCU) class RV32IMC implementation in Verilog.

- SCR1 from Syntacore,[85] a 32-bit microcontroller unit (MCU) class RV32IMC implementation in Verilog.

- MIPT-MIPS[117] by MIPT-ILab (MIPT Lab for CPU Technologies created with help of Intel). MIPT-MIPS is a cycle-accurate pre-silicon simulator of RISC-V and MIPS CPUs. It measures performance of program running on CPU. Among key features are: compatibility with interactive MARS system calls,[118] interactive simulation with GDB, configurable branch prediction unit with several prediction algorithms and instruction cache and interstage data bypassing. Implementation in C++.

- SERV[119] by Olof Kindgren, a physically small, validated bit-serial RV32I core in Verilog, is the world's smallest RISC-V CPU. It is integrated with both the LiteX and FuseSoC SoC construction systems. An FPGA implementation[120] was 125 lookup tables (LUTs) and 164 flip-flops, running at 1.5 MIPS, In a 130 nm-node ASIC, it was 2.1kGE[120] and a high-end FPGA could hold 10,000 cores.[121]

- PULPino (Riscy and Zero-Riscy) from ETH Zürich / University of Bologna.[122] The cores in PULPino implement a simple RV32IMC ISA for microcontrollers (Zero-Riscy) or a more powerful RV32IMFC ISA with custom DSP extensions for embedded signal processing.

- Western Digital, in December 2018 announced an RV32IMC core called SweRV EH1 featuring an in-order 2-way superscalar and nine-stage pipeline design. In December 2019, WD announced the SweRV EH2 an in-order core with two hardware threads and a nine-stage pipeline and the SweRV EL2 a single issue core with a 4-stage pipeline[123] WD plans to use SweRV based processors in their flash controllers and SSDs, and released it as open-source to third parties in January 2019.[124][125][126]

- NEORV32 by Stephan Nolting,[127] a highly-configurable 32-bit microcontroller unit (MCU) class RV32[I/E]MACUX_Zbb_Zfinx_Zicsr_Zifencei CPU with on-chip debugger support written in platform-independent VHDL. The project includes a microcontroller-like SoC that already includes common modules like UART, timers, SPI, TWI, a TRNG and embedded memories.

- Alibaba Group, in July 2019 announced the 2.5 GHz 16-core 64-bit (RV64GCV) XuanTie 910 out-of-order processor.[128] In October 2021 the XuanTie 910 was released as Open-Source.[129]

- The Institute of Computing Technology of the Chinese Academy of Sciences (ICT CAS), in June 2020 launched the XiangShan high-performance RISC-V processor project.[130][131]

Software

A normal problem for a new instruction set is a lack of CPU designs and software — both issues limit its usability and reduce adoption.[11] RISC-V has a large number of CPU designs. RISC-V software includes toolchains, operating systems, middleware[vague] and design software.

Available RISC-V software tools include a GNU Compiler Collection (GCC) toolchain (with GDB, the debugger), an LLVM toolchain, the OVPsim simulator (and library of RISC-V Fast Processor Models), the Spike simulator, and a simulator in QEMU (RV32GC/RV64GC). JEP 422: Linux/RISC-V Port is already integrated into mainline OpenJDK repository.

Operating system support exists for the Linux kernel, FreeBSD, NetBSD, and OpenBSD but the supervisor-mode instructions were unstandardized before version 1.11 of the privileged ISA specification,[2] so this support is provisional. The preliminary FreeBSD port to the RISC-V architecture was upstreamed in February 2016, and shipped in FreeBSD 11.0.[132][98] Ports of the Debian[133] and Fedora[134] Linux distributions, and a port of Haiku,[135] are stabilizing (all only support 64-bit RISC-V, with no plans to support 32-bit version). A port of Das U-Boot exists.[136] UEFI Spec v2.7 has defined the RISC-V binding and a TianoCore port has been done by HPE engineers[137] and is expected to be upstreamed. There is a preliminary port of the seL4 microkernel.[138][139] Hex Five released the first Secure IoT Stack for RISC-V with FreeRTOS support.[140] Also xv6, a modern reimplementation of Sixth Edition Unix in ANSI C used for pedagogical purposes in MIT, was ported. Pharos RTOS has been ported to 64-bit RISC-V[141] (including time and memory protection). Also see Comparison of real-time operating systems.

A simulator exists to run a RISC-V Linux system on a web browser using JavaScript.[142][143][144]

QEMU supports running (using binary translation) 32- and 64-bit RISC-V systems (e.g. Linux) with many emulated or virtualized devices (serial, parallel, USB, network, storage, real time clock, watchdog, audio), as well as running RISC-V Linux binaries (translating syscalls to the host kernel). It does support multi-core emulation (SMP).[145]

The Creator simulator is portable and allows the user to learn various assembly languages of different processors (Creator has examples with an implementation of RISC-V and MIPS32 instructions).[146][147][148][149]

The extensible educational simulator WepSIM implements a (microprogrammed) subset of RISC-V instructions (RV32I+M) and allows the execution of subroutines in assembly.[150][151]

Several languages have been applied to creating RISC-V IP cores including a Scala-based hardware description language, Chisel,[152] which can reduce the designs to Verilog for use in devices, and the CodAL processor description language which has been used in to describe RISC-V processor cores and to generate corresponding HDKs (RTL, testbench and UVM) and SDKs.[153] The RISC-V International Compliance Task Group has a GitHub repository for RV32IMC.[154]

Development tools

- IAR Systems released the first version of IAR Embedded Workbench for RISC-V, which supports RV32 32-bit RISC-V cores and extensions in the first version. Future releases will include 64-bit support and support for the smaller RV32E base instruction set, as well as functional safety certification and security solutions.

- Lauterbach added support for RISC-V to their TRACE32 JTAG debuggers.[155][156] Lauterbach also announced[157] support for SiFives RISC-V NEXUS based processor trace.

- SEGGER released a new product named "J-Trace PRO RISC-V", added support for RISC-V cores to their J-Link debugging probe family,[158] their integrated development environment Embedded Studio,[159] and their RTOS embOS and embedded software.[160]

- UltraSOC, now part of Siemens,[161] proposed a standard trace system and donated an implementation.

See also

Notes

- ↑ Big and bi-endianness supported through non-standard variants; instructions are always little-endian.[1](ppvi, 9–10)

- ↑ The designation V (Roman numeral '5') represents RISC-V as the 5th generation reduced instruction set computer (RISC) architecture that was developed at the University of California, Berkeley since 1981[3]

References

- ↑ 1.00 1.01 1.02 1.03 1.04 1.05 1.06 1.07 1.08 1.09 1.10 1.11 1.12 1.13 1.14 1.15 1.16 1.17 1.18 1.19 1.20 1.21 1.22 1.23 1.24 1.25 1.26 1.27 1.28 1.29 1.30 1.31 1.32 1.33 1.34 1.35 1.36 1.37 1.38 1.39 1.40 1.41 1.42 1.43 1.44 1.45 1.46 1.47 1.48 1.49 1.50 1.51 1.52 1.53 1.54 Waterman, Andrew; Asanović, Krste, eds (December 2019). "The RISC-V Instruction Set Manual, Volume I: User-Level ISA, Document Version 20191213". RISC-V Foundation. https://github.com/riscv/riscv-isa-manual/releases/download/Ratified-IMAFDQC/riscv-spec-20191213.pdf.

- ↑ 2.00 2.01 2.02 2.03 2.04 2.05 2.06 2.07 2.08 2.09 2.10 2.11 Waterman, Andrew; Asanović, Krste (3 December 2021). "The RISC-V Instruction Set Manual Volume II: Privileged Architecture Document Version 20211203". RISC-V International. https://github.com/riscv/riscv-isa-manual/releases/download/Priv-v1.12/riscv-privileged-20211203.pdf.

- ↑ Urquhart, Roddy (29 March 2021). "What Does RISC-V Stand For? A brief history of the open ISA". Systems & Design: Opinion. Semiconductor Engineering. https://semiengineering.com/what-does-risc-v-stand-for/.

- ↑ 4.0 4.1 Waterman, Andrew; Asanović, Krste (7 May 2017). "The RISC-V Instruction Set Manual, Volume I: Base User-Level ISA version 2.2". RISC-V International. https://riscv.org/wp-content/uploads/2017/05/riscv-spec-v2.2.pdf.

- ↑ Newsome, Tim; Wachs, Megan (22 March 2019). "RISC-V External Debug Support Version 0.13.2 d5029366d59e8563c08b6b9435f82573b603e48e". RISC-V International. https://github.com/riscv/riscv-debug-spec/blob/release/riscv-debug-release.pdf.

- ↑ "About RISC-V, RISC-V International is the global non-profit home of the open standard RISC-V Instruction Set Architecture (ISA)". RISC-V International. https://riscv.org/about/.

- ↑ "RISC-V To Move HQ to Switzerland Amid Trade War Concerns". EE Times Europe. 28 November 2019. https://www.eetimes.eu/risc-v-to-move-hq-to-switzerland-amid-trade-war-concerns/.

- ↑ Demerjian, Chuck (August 7, 2013). "A long look at how ARM licenses chips: Part 1". SemiAccurate. https://semiaccurate.com/2013/08/07/a-long-look-at-how-arm-licenses-chips/.

- ↑ Demerjian, Chuck (August 8, 2013). "How ARM licenses its IP for production: Part 2". SemiAccurate. https://semiaccurate.com/2013/08/08/how-arm-licenses-its-ip-for-production/.

- ↑ "Wave Computing Closes Its MIPS Open Initiative with Immediate Effect, Zero Warning". 2019-11-15. https://www.hackster.io/news/wave-computing-closes-its-mips-open-initiative-with-immediate-effect-zero-warning-e88b0df9acd0.

- ↑ 11.0 11.1 11.2 11.3 11.4 11.5 Asanović, Krste. "Instruction Sets Should be Free". Regents of the University of California. https://www2.eecs.berkeley.edu/Pubs/TechRpts/2014/EECS-2014-146.pdf.

- ↑ "Rocket Core Generator". Regents of the University of California. https://riscv.org/download.html#tab_rocket.

- ↑ 13.0 13.1 Celio, Christopher; Love, Eric. "riscv-sodor: educational microarchitectures for risc-v isa". Regents of the University of California. https://github.com/ucb-bar/riscv-sodor.

- ↑ 14.0 14.1 "SHAKTI Processor Program". Indian Institute of Technology Madras. https://shakti.org.in.

- ↑ Celio, Christopher. "CS 152 Laboratory Exercise 3". Regents of the University of California. http://www-inst.eecs.berkeley.edu/~cs152/sp14/handouts/lab3.pdf.

- ↑ 16.0 16.1 16.2 16.3 16.4 Waterman, Andrew; Asanović, Krste (31 May 2016). "The RISC-V Instruction Set Manual, Volume I: Base User-Level ISA version 2.1". University of California, Berkeley. https://www2.eecs.berkeley.edu/Pubs/TechRpts/2016/EECS-2016-118.pdf.

- ↑ 17.0 17.1 Patterson, David A.; Ditzel, David R. (October 1980). "The Case for the Reduced Instruction Set Computer". ACM SIGARCH Computer Architecture News 8 (6): 25. doi:10.1145/641914.641917.

- ↑ "Amber ARM-compatible core". http://opencores.org/project,amber.

- ↑ "ARM4U". http://opencores.org/project,arm4u.

- ↑ Template:Cite tech report

- ↑ Template:Cite tech report

- ↑ Template:Cite tech report

- ↑ "Contributors". Regents of the University of California. https://riscv.org/contributors/.

- ↑ Asanović, Krste. "The RISC-V Instruction Set Manual, Volume I: Base User-Level ISA". Regents of the University of California. https://www2.eecs.berkeley.edu/Pubs/TechRpts/2011/EECS-2011-62.pdf.

- ↑ Hruska, Joel (21 August 2014). "RISC rides again: New RISC-V architecture hopes to battle ARM and x86 by being totally open source". https://www.extremetech.com/computing/188405-risc-rides-again-new-risc-v-architecture-hopes-to-battle-arm-and-x86-by-being-totally-open-source.

- ↑ "RISC-V History". https://riscv.org/about/history/.

- ↑ "A new blueprint for microprocessors challenges the industry's giants". The Economist. 2019-10-03. ISSN 0013-0613. https://www.economist.com/science-and-technology/2019/10/03/a-new-blueprint-for-microprocessors-challenges-the-industrys-giants.

- ↑ "Design Automation Conference". https://dac.com/.

- ↑ "Members" (in en-US). https://riscv.org/members/.

- ↑ "U.S.-based chip-tech group moving to Switzerland over trade curb fears" (in en). Reuters. 2019-11-26. https://www.reuters.com/article/us-usa-china-semiconductors-insight-idUSKBN1XZ16L.

- ↑ Cheung, Sunny (December 15, 2023). "Examining China’s Grand Strategy For RISC-V" (in en-US). Jamestown Foundation. https://jamestown.org/program/examining-chinas-grand-strategy-for-risc-v/.

- ↑ "RISC-V History - RISC-V International". https://riscv.org/risc-v-history/#international.

- ↑ "The Linley Group Announces Winners of Annual Analysts' Choice Awards" (Press release). The Linley Group. 12 January 2017. Retrieved 21 January 2018.

- ↑ 34.0 34.1 "Bit-Manipulation ISA-extensions". RISC-V International. November 2021. https://github.com/riscv/riscv-bitmanip/releases/download/1.0.0/bitmanip-1.0.0-38-g865e7a7.pdf.

- ↑ "Vector Extension". RISC-V International. November 2021. https://github.com/riscv/riscv-v-spec/releases/tag/v1.0.

- ↑ 36.0 36.1 "RISC-V Cryptography Extensions Volume I Scalar & Entropy Source Instructions". 2022-02-18. https://github.com/riscv/riscv-crypto/releases/download/v1.0.1-scalar/riscv-crypto-spec-scalar-v1.0.1.pdf.

- ↑ "RISC-V Profiles". Discussion. 2022. https://github.com/riscv/riscv-profiles/blob/main/profiles.adoc#rva22-profiles.

- ↑ RISC-V Platform Horizontal Subcommittee (December 2021). "RISC-V Platform Specification". https://github.com/riscv/riscv-platform-specs/blob/main/riscv-platform-spec.pdf.

- ↑ 39.0 39.1 39.2 39.3 39.4 39.5 39.6 39.7 39.8 Waterman, Andrew (13 May 2011). Improving Energy Efficiency and Reducing Code Size with RISC-V Compressed. U.C. Berkeley: Regents of the University of California. p. 32. http://www.eecs.berkeley.edu/Pubs/TechRpts/2011/EECS-2011-63.html. Retrieved 25 August 2014.

- ↑ Waterman, Andrew. "The RISC-V Compressed Instruction Set Manual Version 1.9 (draft)". https://riscv.org/wp-content/uploads/2015/11/riscv-compressed-spec-v1.9.pdf.

- ↑ 41.0 41.1 Brussee, Rogier. "A Complete 16-bit RVC". RISC-V Foundation. https://groups.google.com/a/groups.riscv.org/g/isa-dev/c/SrujNcNc8RA/m/0mA-dATSBwAJ.

- ↑ 42.0 42.1 Brussee, Rogier. "Proposal: Xcondensed, [a ... Compact ... 16 bit standalone G-ISA"]. Google Groups. https://groups.google.com/a/groups.riscv.org/g/isa-dev/c/iK3enKGb5bw/m/cuVAq0J8EAAJ.

- ↑ Phung, Xan. "Improved Xcondensed". RISC-V Foundation. https://groups.google.com/a/groups.riscv.org/g/isa-dev/c/SrujNcNc8RA/m/DRDyXTUHAgAJ.

- ↑ Ionescu, Liviu. "The RISC-V Microcontroller Profile". https://github.com/emb-riscv/specs-markdown/blob/master/README.md.

- ↑ Barros, Cesar (1 April 2018). "Proposal: RV16E". RISC-V ISA Developers (Mailing list). Retrieved 2 April 2018.

- ↑ Bonzini, Paolo; Waterman, Andrew. "Proposal for Virtualization without H mode". RISC-V ISA Developers (Mailing list). Retrieved 24 February 2017.

- ↑ "riscv-aclint/riscv-aclint.adoc at main · riscv/riscv-aclint" (in en). https://github.com/riscv/riscv-aclint/blob/main/riscv-aclint.adoc.

- ↑ "RISC-V Bitmanip Extension Document Version 0.93". RISC-V Foundation. 2021-01-10. https://github.com/riscv/riscv-bitmanip/blob/master/bitmanip-0.93.pdf.

- ↑ 49.0 49.1 "Instruction Summary for a "P" ISA Proposal". ANDES Technologies. https://docs.google.com/viewer?a=v&pid=forums&srcid=MDQwMTcyODgwMjc3MjQxMjA0NzcBMDcxOTA2MzQ5OTA0NjY2NzE0MjUBMjVTQUxGc3hCUUFKATAuMQFncm91cHMucmlzY3Yub3JnAXYy.

- ↑ Su, Charlie (30 June 2018). "Comprehensive RISC-V Solutions for AIoT". RISC-V Foundation. https://riscv.org/wp-content/uploads/2018/07/Shanghai-0900-AndesV5-for-AIOT.pdf.

- ↑ 51.0 51.1 51.2 51.3 51.4 51.5 51.6 Schmidt, Colin; Ou, Albert; Lee, Yunsup; Asanović, Krste. "RISC-V Vector Extension Proposal". Regents of the University of California. https://riscv.org/wp-content/uploads/2015/06/riscv-vector-workshop-june2015.pdf.

- ↑ 52.0 52.1 "Release Vector Extension 1.0, frozen for public review · riscv/Riscv-v-spec". https://github.com/riscv/riscv-v-spec/releases/tag/v1.0.